ICSSSTVA16857

Features

:

- Exceeds "SSTVN16857" performance

- Differential clock signal

- Meets SSTL_2 signal data

- Supports SSTL_2 class I & II specifications

- Low-voltage operation

- VDD = 2.3V to 2.7V

- 48 pin TSSOP package

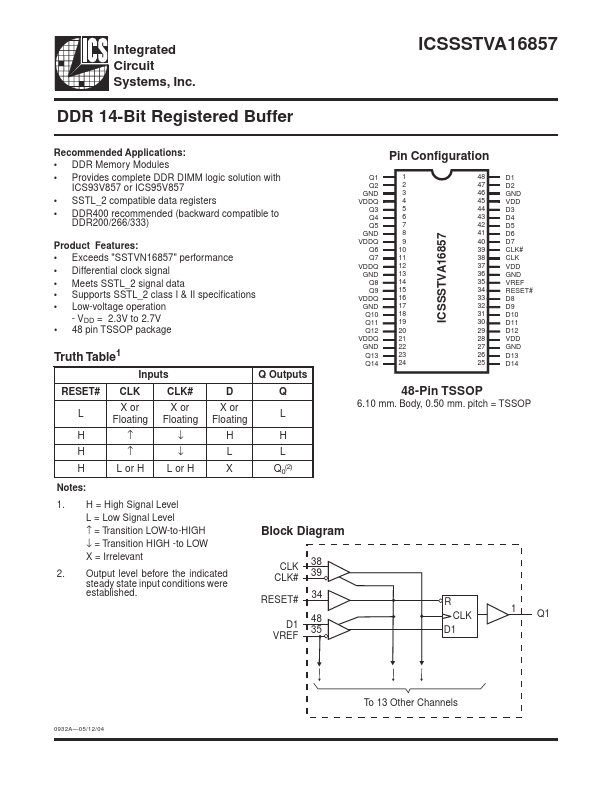

Pin Configuration

Q1 Q2 GND VDDQ Q3 Q4 Q5 GND VDDQ Q6 Q7 VDDQ GND Q8 Q9 VDDQ GND Q10 Q11 Q12 VDDQ GND Q13 Q14 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 D1 D2 GND VDD D3 D4 D5 D6 D7 CLK# CLK VDD GND VREF RESET# D8 D9 D10 D11 D12 VDD GND D13 D14

Truth Table1

Inputs RESET# L H H H

Notes: 1. H = High Signal Level L = Low Signal Level ↑ = Transition LOW-to-HIGH ↓ = Transition HIGH -to LOW X = Irrelevant Output level before the indicated steady state input conditions were established.

Q Outputs D X or Floating H L X Q L H L Q0(2)

CLK X or Floating ↑ ↑ L or H

CLK# X or Floating ↓ ↓ L or H

48-Pin TSSOP

6.10 mm. Body, 0.50 mm. pitch = TSSOP

Block Diagram

CLK CLK# RESET# D1 VREF 38 39...