MK1574 Overview

Description

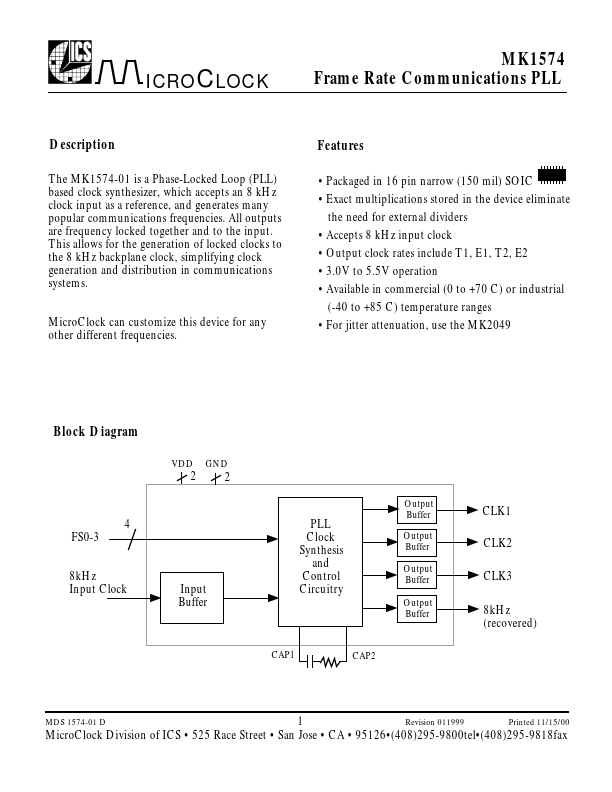

The MK1574-01 is a Phase-Locked Loop (PLL) based clock synthesizer, which accepts an 8 kHz clock input as a reference, and generates many popular communications frequencies. All outputs are frequency locked together and to the input.

Key Features

- Packaged in 16 pin narrow (150 mil) SOIC

- Exact multiplications stored in the device eliminate the need for external dividers

- Accepts 8 kHz input clock

- Output clock rates include T1, E1, T2, E2

- 3.0V to 5.5V operation

- Available in commercial (0 to +70 C) or industrial (-40 to +85 C) temperature ranges

- For jitter attenuation, use the MK2049