MK2049-03 Overview

Description

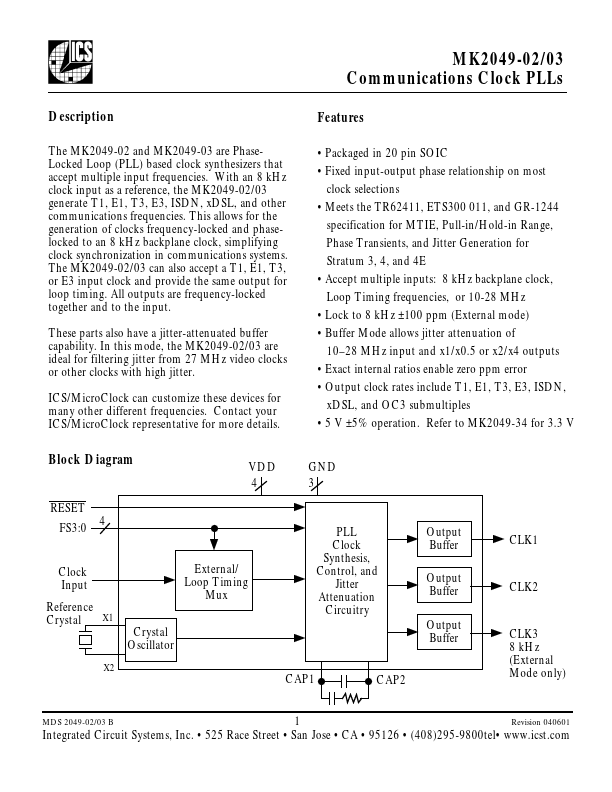

The MK2049-02 and MK2049-03 are PhaseLocked Loop (PLL) based clock synthesizers that accept multiple input frequencies. With an 8 kHz clock input as a reference, the MK2049-02/03 generate T1, E1, T3, E3, ISDN, xDSL, and other communications frequencies.

Key Features

- Packaged in 20 pin SOI