MK74ZD133

Features

- 56 pin SSOP or 64 pin LQFP package

- On-chip PLL generates output clocks up to 80 MHz (SSOP) or 133.33 MHz (LQFP)

- Zero delay plus multiplier function

- 32 low-skew outputs can eliminate chip-to-chip skew concerns in systems with less than 33 clocks

- Output to output skew of 200 ps (with stagger)

- Device to device skew of 700ps

- Staggered, fixed skew helps reduce EMI

- Tri-state (Output Enable) pin

- Output blocks can be independently powered off

- 250 ps typical fixed delay between input and output in “Multiplier” mode

- Ideal for Fast Ethernet and Gigabit Ethernet designs

- Good for video servers

- 3.3V±5% supply voltage

Description

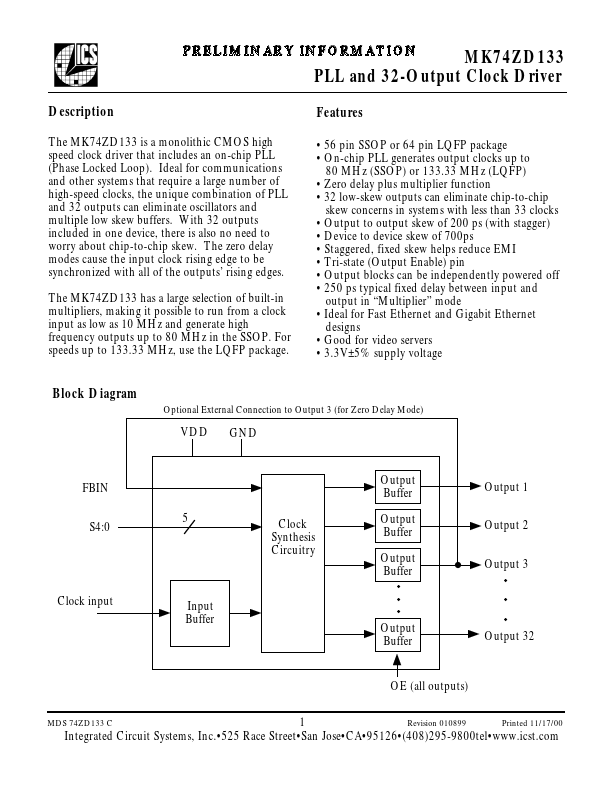

The MK74ZD133 is a monolithic CMOS high speed clock driver that includes an on-chip PLL (Phase Locked Loop). Ideal for munications and other systems that require a large number of high-speed clocks, the unique bination of PLL and 32 outputs can eliminate oscillators and multiple low skew buffers. With 32 outputs included in one device,...