IDT74FCT162260AT

IDT74FCT162260AT is FAST CMOS 12-BIT TRI-PORT BUS EXCHANGER manufactured by Integrated Device Tech.

FAST CMOS 12-BIT TRI-PORT BUS EXCHANGER

Integrated Device Technology, Inc.

IDT54/74FCT16260AT/CT/ET IDT54/74FCT162260AT/CT/ET

Features

:

- mon Features

:

- 0.5 MICRON CMOS Technology

- High-speed, low-power CMOS replacement for ABT functions

- Typical t SK(o) (Output Skew) < 250ps

- Low input and output leakage ≤1µ A (max.)

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack

- Extended mercial range of -40°C to +85°C

- VCC = 5V ±10%

- Features for FCT16260AT/CT/ET:

- High drive outputs (-32m A IOH, 64m A IOL)

- Power off disable outputs permit “live insertion”

- Typical VOLP (Output Ground Bounce) < 1.0V at VCC = 5V, TA = 25°C

- Features for FCT162260AT/CT/ET:

- Balanced Output Drivers: ±24m A (mercial), ±16m A (military)

- Reduced system switching noise

- Typical VOLP (Output Ground Bounce) < 0.6V at VCC = 5V,TA = 25°C

DESCRIPTION:

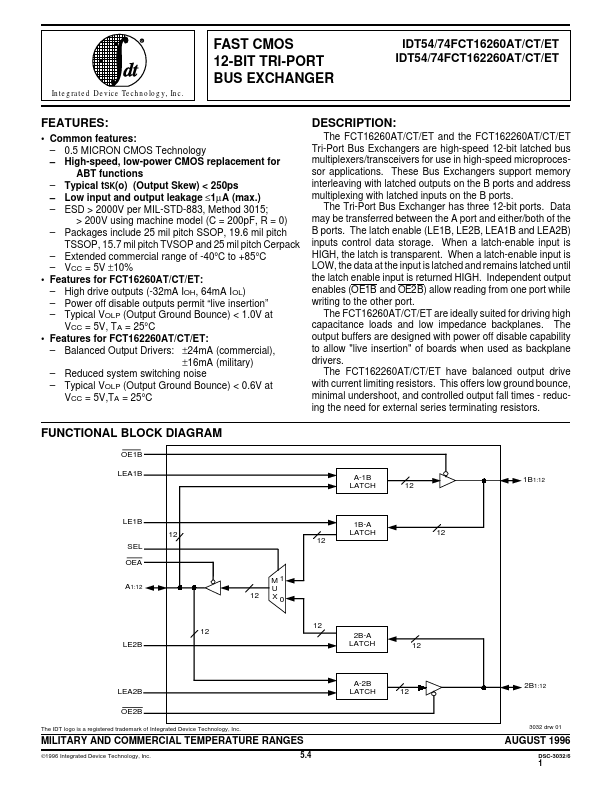

The FCT16260AT/CT/ET and the FCT162260AT/CT/ET Tri-Port Bus Exchangers are high-speed 12-bit latched bus multiplexers/transceivers for use in high-speed microprocessor applications. These Bus Exchangers support memory interleaving with latched outputs on the B ports and address multiplexing with latched inputs on the B ports. The Tri-Port Bus Exchanger has three 12-bit ports. Data may be transferred between the A port and either/both of the B ports. The latch enable (LE1B, LE2B, LEA1B and LEA2B) inputs control data storage. When a latch-enable input is HIGH, the latch is transparent. When a latch-enable input is LOW, the data at the input is latched and remains latched until the latch enable input is returned HIGH. Independent output enables (OE1B and OE2B) allow reading from one port while writing to the other port. The FCT16260AT/CT/ET are ideally suited for driving high capacitance loads and low impedance backplanes. The output buffers are designed with power off disable capability to...