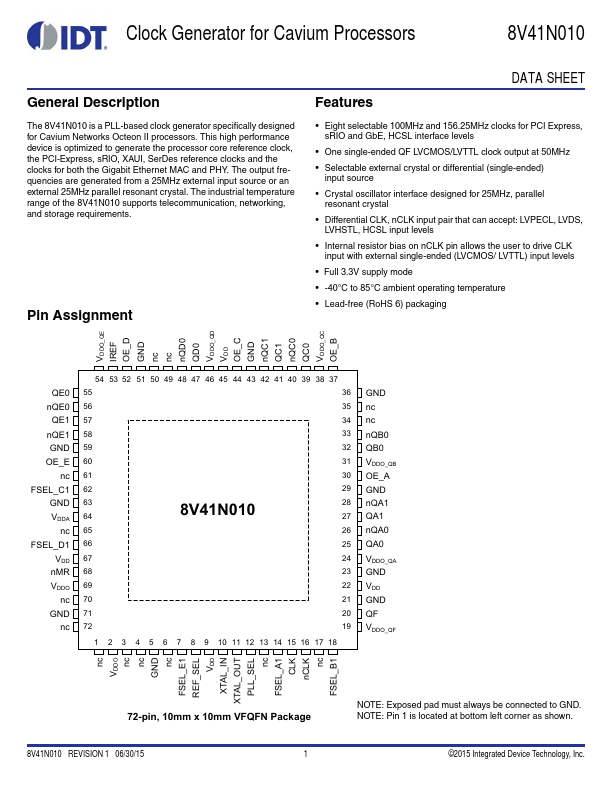

8V41N010

Description

The 8V41N010 is a PLL-based clock generator specifically designed for Cavium Networks Octeon II processors.

Key Features

- Eight selectable 100MHz and 156.25MHz clocks for PCI Express, sRIO and GbE, HCSL interface levels

- One single-ended QF LVCMOS/LVTTL clock output at 50MHz

- Selectable external crystal or differential (single-ended) input source

- Crystal oscillator interface designed for 25MHz, parallel resonant crystal

- Differential CLK, nCLK input pair that can accept: LVPECL, LVDS, LVHSTL, HCSL input levels

- Internal resistor bias on nCLK pin allows the user to drive CLK input with external single-ended (LVCMOS/ LVTTL) input levels

- Full 3.3V supply mode

- 40°C to 85°C ambient operating temperature