AN-136 Overview

Description

The 71215 and 71216 represent a new generation of integrated Tag SRAMs. Just as earlier Tag SRAMs such as the 71B74 were better suited for tag applications than conventional SRAMs, the 71215/16 go a step further by integrating new features to significantly ease the design of high performance cache subsystems for today’s high speed processors.

Key Features

- to significantly ease the design of high performance cache subsystems for today’s high speed processors

- Since the 71215 and 71216 are very similar, the descriptions and explanations in this application note apply to both unless otherwise noted

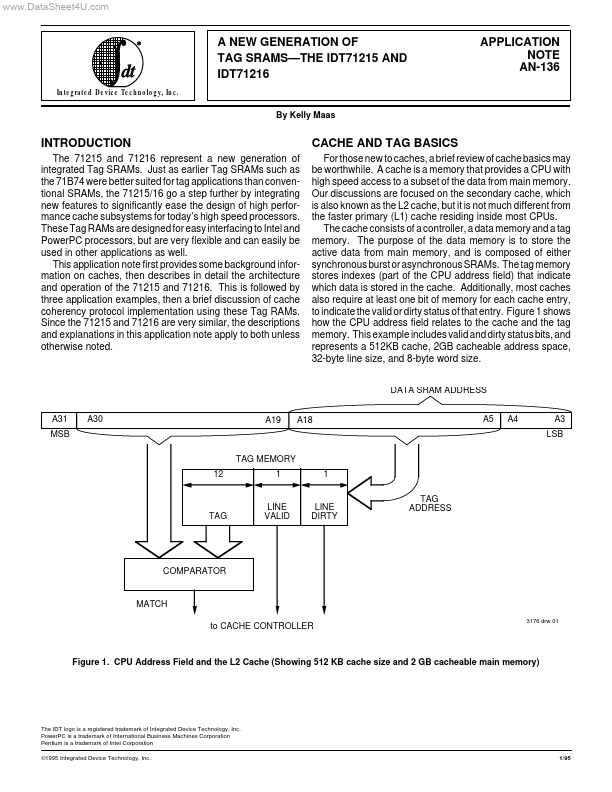

- CACHE AND TAG BASICS For those new to caches, a brief review of cache basics may be worthwhile

- A cache is a memory that provides a CPU with high speed access to a subset of the data from main memory

- The cache consists of a controller, a data memory and a tag memory