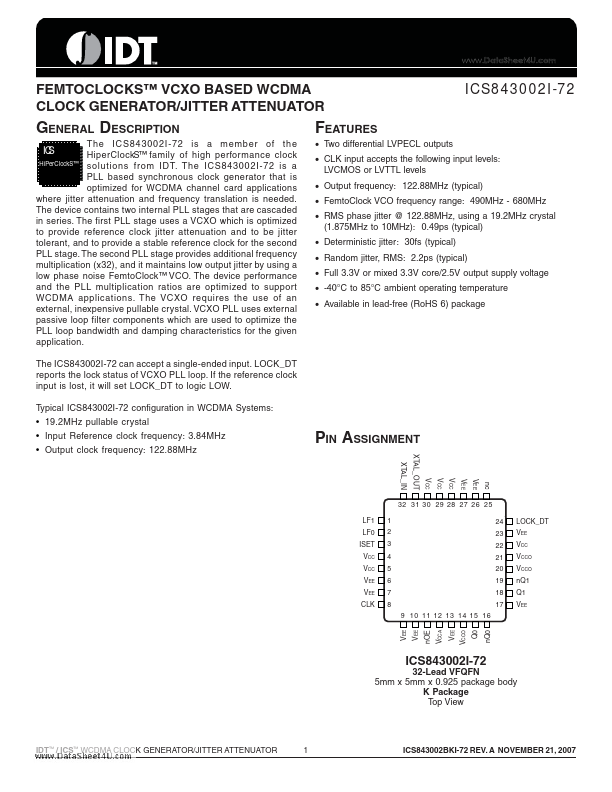

ICS843002I-72

Description

The ICS843002I-72 is a member of the IC S HiperClockS™ family of high performance clock HiPerClockS™ solutions from IDT. The ICS843002I-72 is a PLL based synchronous clock generator that is optimized for WCDMA channel card applications where jitter attenuation and frequency translation is needed.

Key Features

- Two differential LVPECL outputs

- CLK input accepts the following input levels: LVCMOS or LVTTL levels

- Output frequency: 122.88MHz (typical)

- FemtoClock VCO frequency range: 490MHz - 680MHz

- RMS phase jitter @ 122.88MHz, using a 19.2MHz crystal (1.875MHz to 10MHz): 0.49ps (typical)

- Deterministic jitter: 30fs (typical)

- Random jitter, RMS: 2.2ps (typical)

- Full 3.3V or mixed 3.3V core/2.5V output supply voltage

- -40°C to 85°C ambient operatin