ICS874003-05

ICS874003-05 is PCI EXPRESS JITTER ATTENUATOR manufactured by Integrated Device Technology.

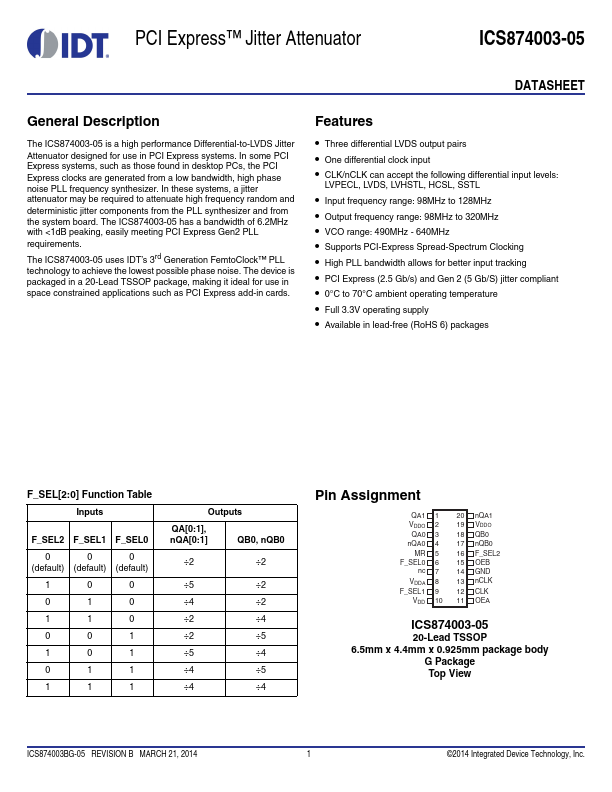

PCI Express™ Jitter Attenuator

General Description

The ICS874003-05 is a high performance Differential-to-LVDS Jitter Attenuator designed for use in PCI Express systems. In some PCI Express systems, such as those found in desktop PCs, the PCI Express clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter ponents from the PLL synthesizer and from the system board. The ICS874003-05 has a bandwidth of 6.2MHz with <1dB peaking, easily meeting PCI Express Gen2 PLL requirements.

The ICS874003-05 uses IDT’s 3rd Generation...