ICS98ULPA877A

Description

/Features

:

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_18)

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- Auto PD when input signal is at a certain logic state Switching Characteristics:

- Period jitter: 40ps (DDR2-400/533) 30ps (DDR2-667/800)

- Half-period jitter: 60ps (DDR2-400/533) 50ps (DDR2-667/800)

- OUTPUT

- OUTPUT skew: 40ps (DDR2-400/533) 30ps (DDR2-667/800)

- CYCLE

- CYCLE jitter 40ps

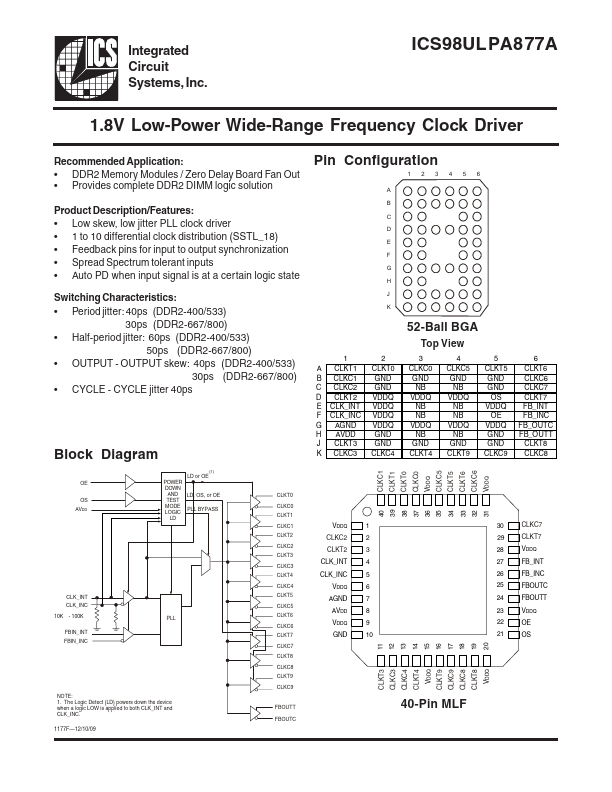

Pin Configuration

1 A B C D E F G H J K 2 3 4 5 6

52-Ball BGA

Top View

A B C D E F G H J K 1 CLKT1 CLKC1 CLKC2 CLKT2 CLK_INT CLK_INC AGND AVDD CLKT3 CLKC3 2 CLKT0 GND GND VDDQ VDDQ VDDQ VDDQ GND GND CLKC4

CLKC1 CLKC0 CLKT1

Block Diagram

OE OS AVDD LD or OE POWER DOWN AND LD, OS, or OE TEST MODE PLL BYPASS LOGIC LD

(1)

3 CLKC0 GND NB VDDQ NB NB VDDQ NB GND CLKT4

CLKC5 CLKT0 VDDQ

4 CLKC5 GND NB VDDQ NB NB VDDQ NB GND CLKT9

CLKT5 CLKC6 CLKT6

5 CLKT5 GND GND OS VDDQ OE VDDQ GND GND CLKC9

VDDQ

6...