IDT54FCT3573

IDT54FCT3573 is 3.3V CMOS OCTAL TRANSPARENT LATCHES manufactured by Integrated Device Technology.

3.3V CMOS OCTAL TRANSPARENT LATCHES

Integrated Device Technology, Inc.

IDT54/74FCT3573/A ADVANCE INFORMATION

Features

:

- 0.5 MICRON CMOS Technology

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- 25 mil Center SSOP Packages

- Extended mercial range of -40°C to +85°C

- VCC = 3.3V ± 0.3V, Normal Range or VCC = 2.7V to 3.6V, Extended Range

- CMOS power levels (0.4µW typ. static)

- Rail-to-Rail output swing for increased noise margin

- Military product pliant to MIL-STD-883, Class B

DESCRIPTION:

The FCT3573/A are octal transparent latches built using an advanced dual metal CMOS technology. These octal latches have 3-state outputs and are intended for bus oriented applications. The flip-flops appear transparent to the data when Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the set-up time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the bus output is in the high-impedance state.

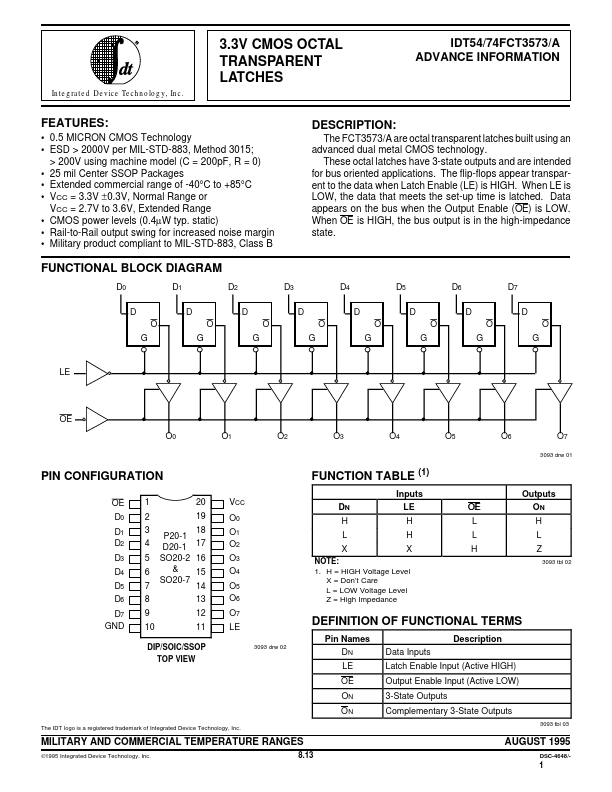

FUNCTIONAL BLOCK DIAGRAM

D0 D O G G D1 D O G D2 D O G D3 D O G D4 D O G D5 D O G D6 D O G D7 D O

OE O0 O1 O2 O3 O4 O5 O6 O7

3093 drw 01

PIN CONFIGURATION

OE D0 D1 D2 D3 D4 D5 D6 D7 GND 1 2 3 4 5 6 7 8 9 10 20 19 P20-1 D20-1 17 SO20-2 16 & 15 SO20-7 14 13 12 11 18 VCC O0 O1 O2 O3 O4 O5 O6 O7 LE

3093 drw 02

FUNCTION TABLE (1)

DN H L X Inputs LE H H X

Outputs ON H L Z

3093 tbl 02

NOTE: 1. H = HIGH Voltage Level X = Don’t Care L = LOW Voltage Level Z = High Impedance

DEFINITION OF FUNCTIONAL TERMS

Pin Names DN LE Description Data Inputs Latch Enable Input (Active HIGH) Output Enable Input (Active LOW) 3-State Outputs plementary 3-State Outputs

3093 tbl...