IDT70T9359 Description

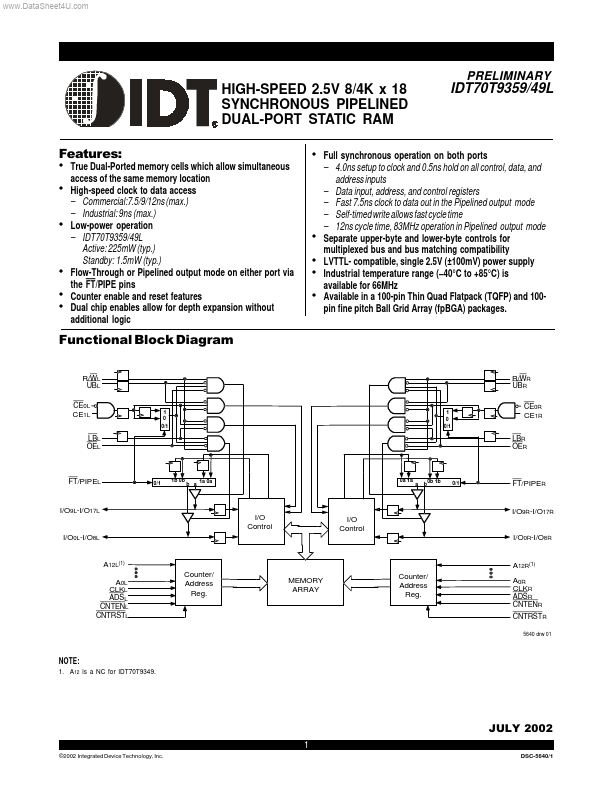

The IDT70T9359/49 is a high-speed 8/4K x 18 bit synchronous Dual-Port RAM. The memory array utilizes Dual-Port memory cells to allow simultaneous access of any address from both ports. Registers on control, data, and address inputs provide minimal setup and hold times.

IDT70T9359 Key Features

- 4.0ns setup to clock and 0.5ns hold on all control, data, and address inputs

- Data input, address, and control registers

- Fast 7.5ns clock to data out in the Pipelined output mode

- Self-timed write allows fast cycle time