IDT71216 Overview

Description

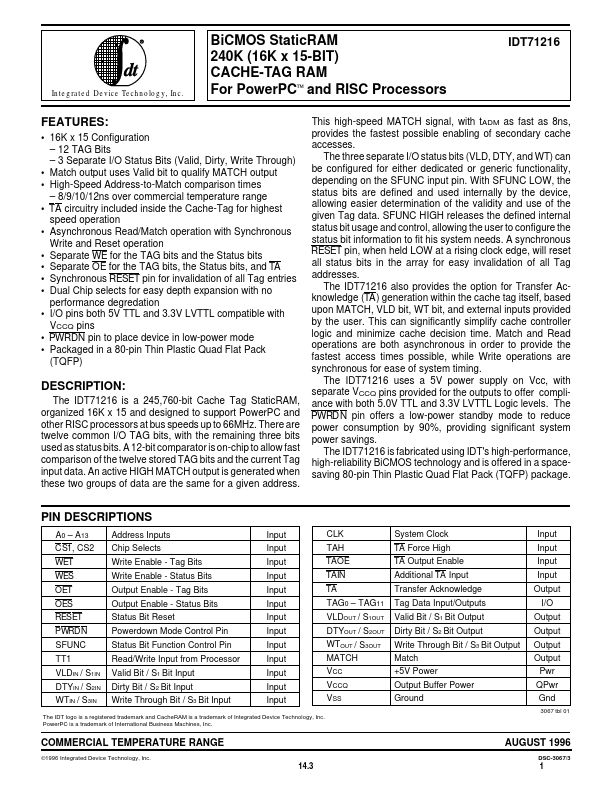

The IDT71216 is a 245,760-bit Cache Tag StaticRAM, organized 16K x 15 and designed to support PowerPC and other RISC processors at bus speeds up to 66MHz. There are twelve common I/O TAG bits, with the remaining three bits used as status bits.

Key Features

- 16K x 15 Configuration – 12 TAG Bits – 3 Separate I/O Status Bits (Valid, Dirty, Write Through)

- Match output uses Valid bit to qualify MATCH output

- High-Speed Address-to-Match comparison times – 8/9/10/12ns over commercial temperature range

- TA circuitry included inside the Cache-Tag for highest speed operation

- Asynchronous Read/Match operation with Synchronous Write and Reset operation

- Separate WE for the TAG bits and the Status bits

- Separate OE for the TAG bits, the Status bits, and TA

- Synchronous RESET pin for invalidation of all Tag entries

- Dual Chip selects for easy depth expansion with no performance degredation

- I/O pins both 5V TTL and 3.3V LVTTL compatible with VCCQ pins