IDT72510

IDT72510 is BUS-MATCHING BIDIRECTIONAL FIFO 512 x 18-BIT . 1024 x 9-BIT 1024 x 18-BIT . 2048 x 9-BIT manufactured by Integrated Device Technology.

Integrated Device Technology, Inc.

BUS-MATCHING BIDIRECTIONAL FIFO 512 x 18-BIT

- 1024 x 9-BIT 1024 x 18-BIT

- 2048 x 9-BIT

DESCRIPTION:

IDT72510 IDT72520

Features

:

- Two side-by-side FIFO memory arrays for bidirectional data transfers

- 512 x 18-Bit

- 1024 x 9-Bit (IDT72510)

- 1024 x 18-Bit

- 2048 x 9-Bit (IDT72520)

- 18-bit data bus on Port A side and 9-bit data bus on Port B side

- Can be configured for 18-to-9-bit, 36-to-9-bit, or 36-to-18bit munication

- Fast 25ns access time

- Fully programmable standard microprocessor interface

- Built-in bypass path for direct data transfer between two ports

- Two fixed flags, Empty and Full, for both the A-to-B and the B-to-A FIFO

- Two programmable flags, Almost-Empty and Almost-Full for each FIFO

- Programmable flag offset can be set to any depth in the FIFO

- Any of the eight internal flags can be assigned to four external flag pins

- Flexible reread/rewrite capabilities.

- On-chip parity checking and generation

- Standard DMA control pins for data exchange with peripherals

- IDT72510 and IDT72520 available in the the 52-pin PLCC package

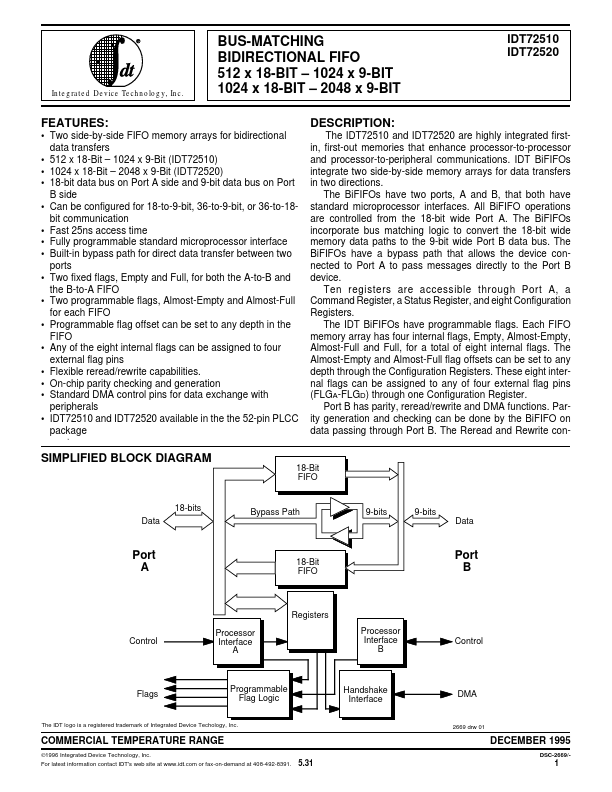

The IDT72510 and IDT72520 are highly integrated firstin, first-out memories that enhance processor-to-processor and processor-to-peripheral munications. IDT Bi FIFOs integrate two side-by-side memory arrays for data transfers in two directions. The Bi FIFOs have two ports, A and B, that both have standard microprocessor interfaces. All Bi FIFO operations are controlled from the 18-bit wide Port A. The Bi FIFOs incorporate bus matching logic to convert the 18-bit wide memory data paths to the 9-bit wide Port B data bus. The Bi FIFOs have a bypass path that allows the device connected to Port A to pass messages directly to the Port B device. Ten registers are accessible through Port A, a mand Register, a Status Register, and eight Configuration Registers. The IDT Bi FIFOs have programmable flags. Each FIFO memory array has four internal flags, Empty, Almost-Empty, Almost-Full and...