IDT72P51569

Key Features

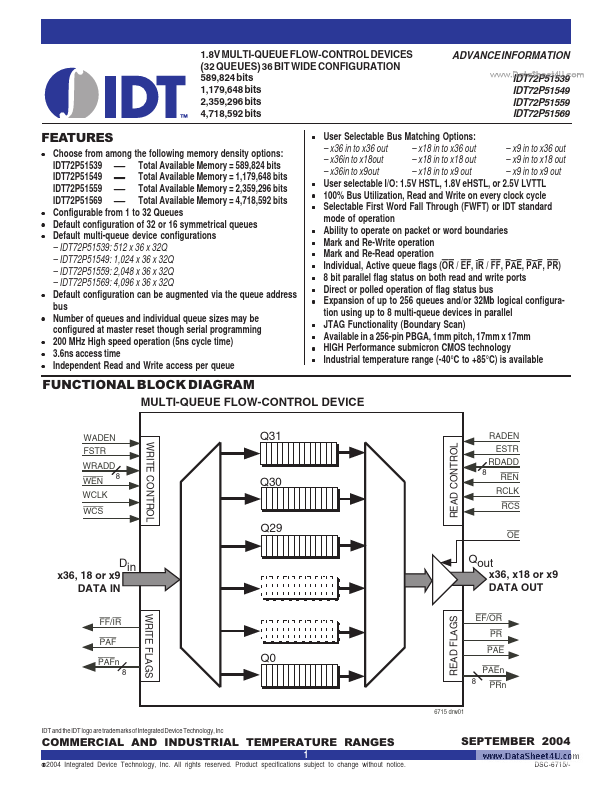

- Choose from among the following memory density options: IDT72P51539 Total Available Memory = 589,824 bits IDT72P51549 Total Available Memory = 1,179,648 bits IDT72P51559 Total Available Memory = 2,359,296 bits IDT72P51569 Total Available Memory = 4,718,592 bits Configurable from 1 to 32 Queues Default configuration of 32 or 16 symmetrical queues Default multi-queue device configurations - IDT72P51539: 512 x 36 x 32Q - IDT72P51549: 1,024 x 36 x 32Q - IDT72P51559: 2,048 x 36 x 32Q - IDT72P51569: 4,096 x 36 x 32Q Default configuration can be augmented via the queue address bus Number of queues and individual queue sizes may be configured at master reset though serial programming 200 MHz High speed operation (5ns cycle time) 3.6ns access time Independent Read and Write access per queue * * * * * * * * * * * * *

- User Selectable Bus Matching Options: - x36 in to x36 out - x18 in to x36 out - x9 in to x36 out - x36in to x18out - x18 in to x18 out - x9 in to x18 out - x36in to x9out - x18 in to x9 out - x9 in to x9 out User selectable I/O: 1.5V HSTL, 1.8V eHSTL, or 2.5V LVTTL 100% Bus Utilization, Read and Write on every clock cycle Selectable First Word Fall Through (FWFT) or IDT standard mode of operation Ability to operate on packet or word boundaries Mark and Re-Write operation Mark and Re-Read operation Individual, Active queue flags (OR / EF, IR / FF, PAE, PAF, PR) 8 bit parallel flag status on both read and write ports Direct or polled operation of flag status bus Expansion of up to 256 queues and/or 32Mb logical configuration using up to 8 multi-queue devices in parallel JTAG Functionality (Boundary Scan) Available in a