IDT72V2105

IDT72V2105 is CMOS FIFO memories manufactured by Integrated Device Technology.

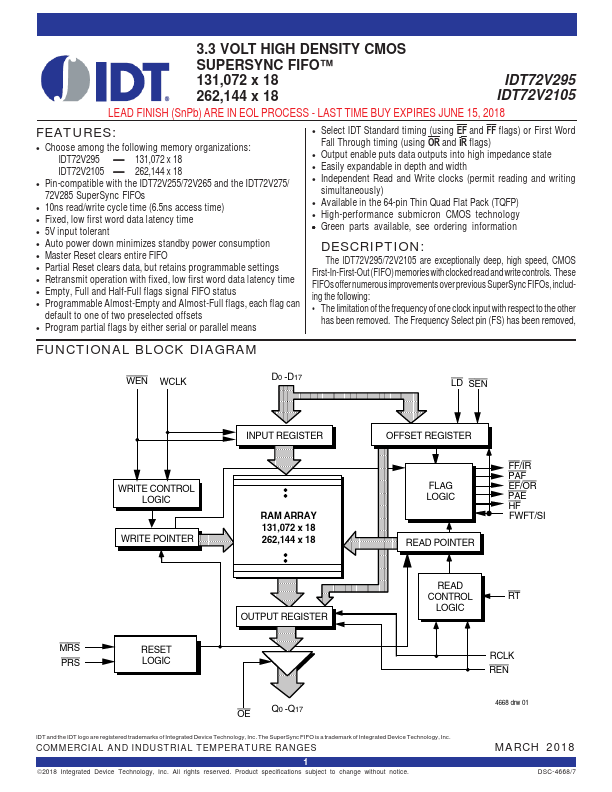

3.3 VOLT HIGH DENSITY CMOS SUPERSYNC FIFO™ 131,072 x 18 262,144 x 18

.EATURES:

- -

- -

- -

- IDT72V295 IDT72V2105

- -

- -

- -

- -

- -

- Choose among the following memory organizations: IDT72V295 131,072 x 18 IDT72V2105 262,144 x 18 Pin-patible with the IDT72V255/72V265 and the IDT72V275/ 72V285 SuperSync FIFOs 10ns read/write cycle time (6.5ns access time) Fixed, low first word data latency time 5V input tolerant Auto power down minimizes standby power consumption Master Reset clears entire FIFO Partial Reset clears data, but retains programmable settings Retransmit operation with fixed, low first word data latency time Empty, Full and Half-Full flags signal FIFO status...