IDT74ALVCH16901

IDT74ALVCH16901 is 3.3V CMOS 18-BIT UNIVERSAL BUS TRANSCEIVER manufactured by Integrated Device Technology.

IDT74ALVCH16901 3.3V CMOS 18-BIT UNIVERSAL BUS TRANSCEIVER WITH PARITY

INDUSTRIAL TEMPERATURE RANGE

3.3V CMOS 18-BIT IDT74ALVCH16901 UNIVERSAL BUS TRANSCEIVER WITH PARITY GENERATORS/ CHECKERS AND BUS-HOLD

- 0.5 MICRON CMOS Technology

- Typical t SK(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range ..

- VCC = 2.5V ± 0.2V

- CMOS power levels (0.4µ W typ. static)

- Rail-to-Rail output swing for increased noise margin

- Available in TSSOP package

Features

:

DESCRIPTION:

DRIVE Features

:

- High Output Drivers: ±24m A

- Suitable for heavy loads

APPLICATIONS:

- 3.3V high speed systems

- 3.3V and lower voltage puting systems

This 18-bit universal bus transceiver is built using advanced dual metal CMOS technology. The ALVCH16901 is a dual 9-bit to dual 9-bit parity transceiver with registers. The device can operate as a feed-through transceiver or it can generate/check parity from the two 8-bit data buses in either direction. The ALVCH16901 Features independent clock (CLKAB or CLKBA), latch-enable (LEAB or LEBA), and dual 9-bit clock enable (CLKENAB or CLKENBA) inputs. It also provides parity-enable (SEL) and parity-select (ODD/EVEN) inputs and separate error-signal (ERRA and ERRB) outputs for checking parity. The direction of data flow is controlled by OEAB and OEBA. When SEL is low, the parity functions are enabled. When SEL is high, the parity functions are disabled and the device acts as an 18-bit registered transceiver. The ALVCH16901 has been designed with a ±24m A output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance. The ALVCH16901 has “bus-hold” which retains the inputs’ last state whenever the input bus goes to a high impedance. This prevents floating inputs and eliminates the need for pull-up/down resistors.

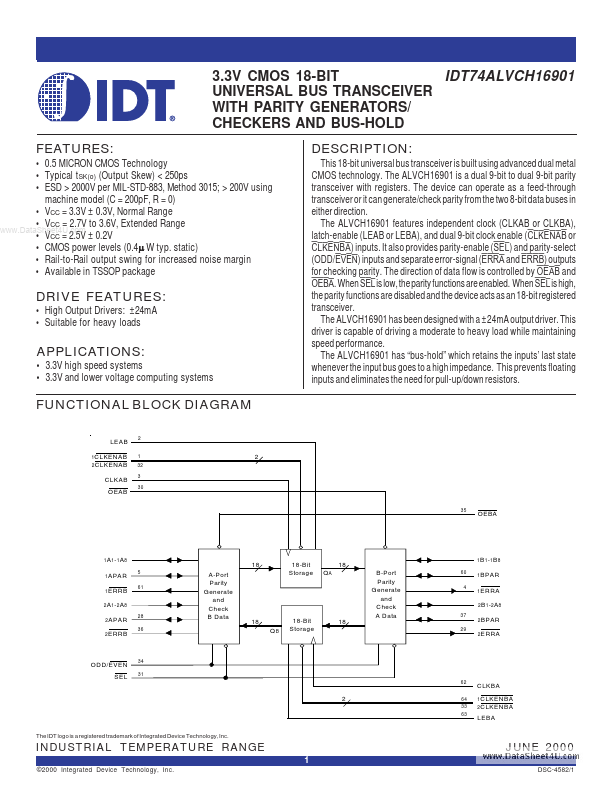

FUNCTIONAL BLOCK DIAGRAM

LEAB

1 CLKENAB 2...