IDT74AUC16373

IDT74AUC16373 is 1.8V CMOS 16-BIT TRANSPARENT D-TYPE LATCH manufactured by Integrated Device Technology.

..

IDT74AUC16373 1.8V CMOS 16-BIT TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS

INDUSTRIAL TEMPERATURE RANGE

1.8V CMOS 16-BIT TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS

Features

: DESCRIPTION:

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- 1.8V Optimized

- 0.8V to 2.7V Operating Range

- Inputs/outputs tolerant up to 3.6V

- Output drivers: ±9m A @ 2.3V

- Supports hot insertion

- Available in TSSOP, TVSOP, and VFBGA packages

APPLICATIONS:

- high performance, low voltage munications systems

- high performance, low voltage puting systems

This 16-bit transparent D-type latch is built using advanced CMOS technology. The device can be used as a single 16-bit latch or as two 8-bit latches. When the latch enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the levels set up at the D inputs. A buffered output enable (OE) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The OE input does not affect the internal operation of the latch. This device is fully specified for partial power-down applications using IOFF. The IOFF circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. To ensure the high-impedance state during power up or power down, OE should be tied to VDD through a pull-up resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

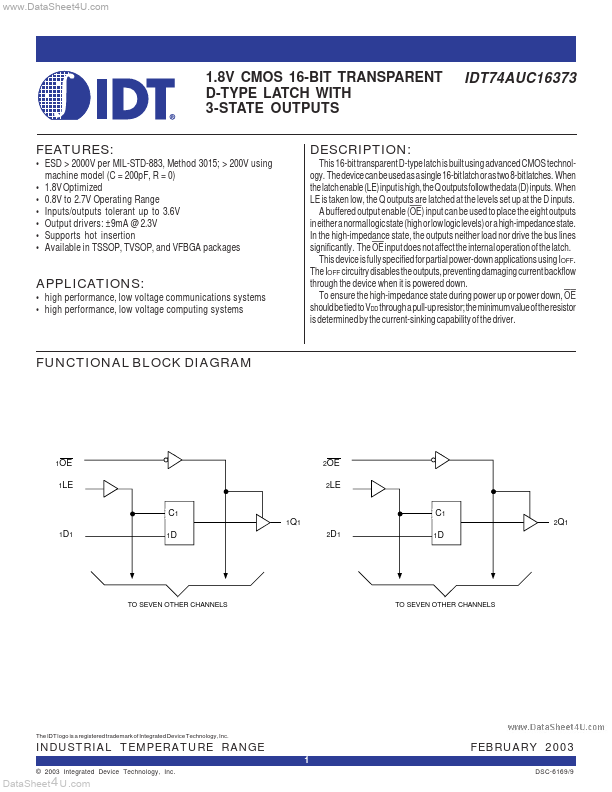

FUNCTIONAL BLOCK DIAGRAM

1OE 1LE

2OE 2LE

C1

1Q1 1D 1 1D 2D1

C1

2Q 1 1D

TO SEVEN OTHER CHANNELS

TO SEVEN OTHER CHANNELS

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

© 2003 Integrated Device Technology, Inc.

FEBRUARY...