IDT74FCT388915T133

IDT74FCT388915T133 is 3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER WITH manufactured by Integrated Device Technology.

- Part of the IDT-74FCT comparator family.

- Part of the IDT-74FCT comparator family.

IDT54/74FCT388915T 70/100/133/150 3.3V LOW SKEW PLL-BASED CLOCK DRIVER

MILITARY AND MERCIAL TEMPERATURE RANGES

Integrated Device Technology, Inc.

3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER (WITH 3-STATE)

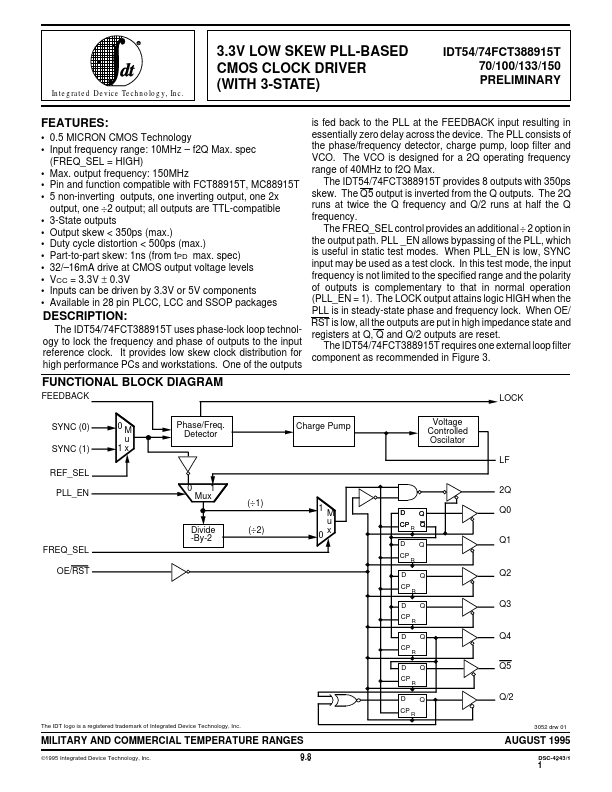

IDT54/74FCT388915T 70/100/133/150 PRELIMINARY is fed back to the PLL at the FEEDBACK input resulting in essentially zero delay across the device. The PLL consists of

- 0.5 MICRON CMOS Technology the phase/frequency detector, charge pump, loop filter and

- Input frequency range: 10MHz

- f2Q Max. spec VCO. The VCO is designed for a 2Q operating frequency (FREQ_SEL = HIGH) range of 40MHz to f2Q Max.

- Max. output frequency: 150MHz The IDT54/74FCT388915T provides 8 outputs with 350ps

-...