IDT74FCT3932-100

IDT74FCT3932-100 is 3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER manufactured by Integrated Device Technology.

Features

:

- -

- -

- 0.5 MICRON CMOS Technology Guaranteed low skew 16 programmable frequency configurations 17 3-state outputs: ±24 m A FCT3932 ±8 m A FCT32932 Output configuration: BANK1: 4 outputs BANK2: 8 outputs BANK3: 5 outputs Dedicated feedback output (Q_FB) Maximum output frequency: 100MHz VCC = 3.3V ±0.3V Inputs can be driven from 3.3V or 5V ponents Available in 48 SSOP, TSSOP packages Suited to SDRAM applications

- -

- -

- -

DESCRIPTION:

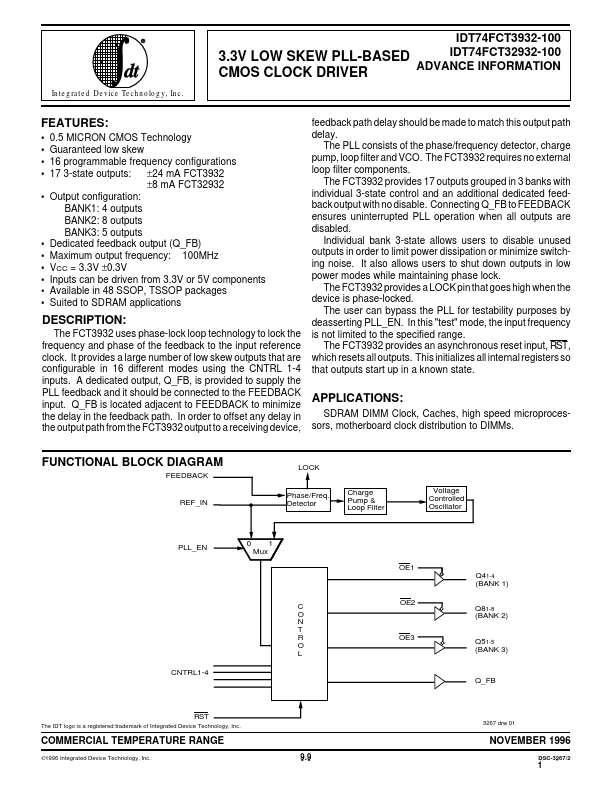

The FCT3932 uses phase-lock loop technology to lock the frequency and phase of the feedback to the input reference clock. It provides a large number of low skew outputs that are configurable in 16 different modes using the CNTRL 1-4 inputs. A dedicated output, Q_FB, is provided to supply the PLL feedback and it should be connected to the FEEDBACK input. Q_FB is located adjacent to FEEDBACK to minimize the delay in the feedback path. In order to offset any delay in the output path from the FCT3932 output to a receiving device, feedback path delay should be made to match this output path delay. The PLL consists of the phase/frequency detector, charge pump, loop filter and VCO. The FCT3932 requires no external loop filter ponents. The FCT3932 provides 17 outputs grouped in 3 banks with individual 3-state control and an additional dedicated feedback output with no disable. Connecting Q_FB to FEEDBACK ensures uninterrupted PLL operation when all outputs are disabled. Individual bank 3-state allows users to disable unused outputs in order to limit power dissipation or minimize switching noise. It also allows users to shut down outputs in low power modes while maintaining phase lock. The FCT3932 provides a LOCK pin that goes high when the device is phase-locked. The user can bypass the PLL for testability purposes by deasserting PLL_EN. In this "test" mode, the input frequency is not limited to the specified range. The FCT3932 provides an asynchronous reset input, , which resets all outputs. This initializes all internal...