IDT74LVCH16501A

IDT74LVCH16501A is 3.3V CMOS 18-BIT REGISTERED BUS TRANSCEIVER manufactured by Integrated Device Technology.

IDT74LVCH16501A 3.3V CMOS 18-BIT REGISTERED TRANSCEIVER WITH 5 VOLT I/O

INDUSTRIAL TEMPERATURE RANGE

3.3V CMOS 18-BIT IDT74LVCH16501A REGISTERED BUS TRANSCEIVER WITH 5V TOLERANT I/O AND BUS-HOLD

- Typical t SK(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range

- CMOS power levels (0.4µ W typ. static) ..

- All inputs, outputs, and I/O are 5V tolerant

- Supports hot insertion

- Available in SSOP and TSSOP packages

Features

:

DESCRIPTION:

DRIVE Features

: APPLICATIONS:

- High Output Drivers: ±24m A

- Reduced system switching noise

- 5V and 3.3V mixed voltage systems

- Data munication and telemunication systems

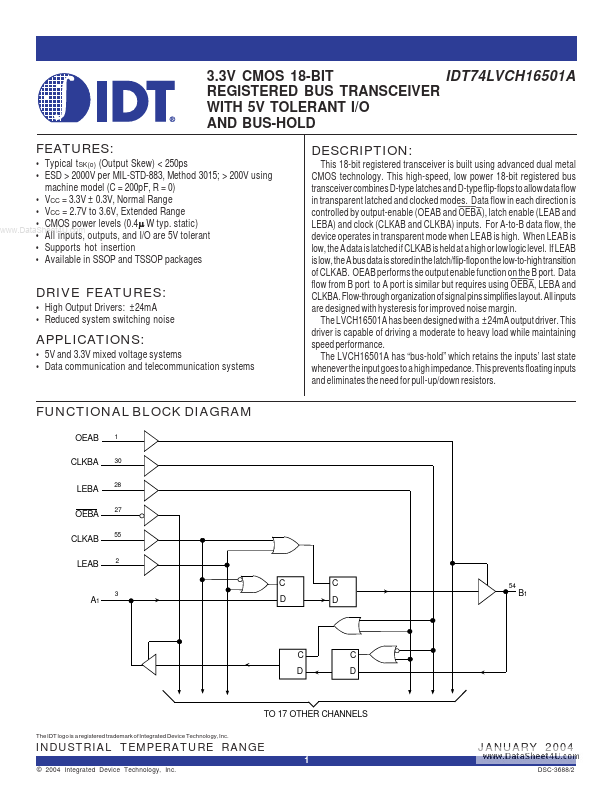

This 18-bit registered transceiver is built using advanced dual metal CMOS technology. This high-speed, low power 18-bit registered bus transceiver bines D-type latches and D-type flip-flops to allow data flow in transparent latched and clocked modes. Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch enable (LEAB and LEBA) and clock (CLKAB and CLKBA) inputs. For A-to-B data flow, the device operates in transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A bus data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. OEAB performs the output enable function on the B port. Data flow from B port to A port is similar but requires using OEBA, LEBA and CLKBA. Flow-through organization of signal pins simplifies layout. All inputs are designed with hysteresis for improved noise margin. The LVCH16501A has been designed with a ±24m A output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance. The LVCH16501A has “bus-hold” which retains the inputs’ last state whenever the input goes to a high impedance. This prevents...