IDT8T33FS314I

Overview

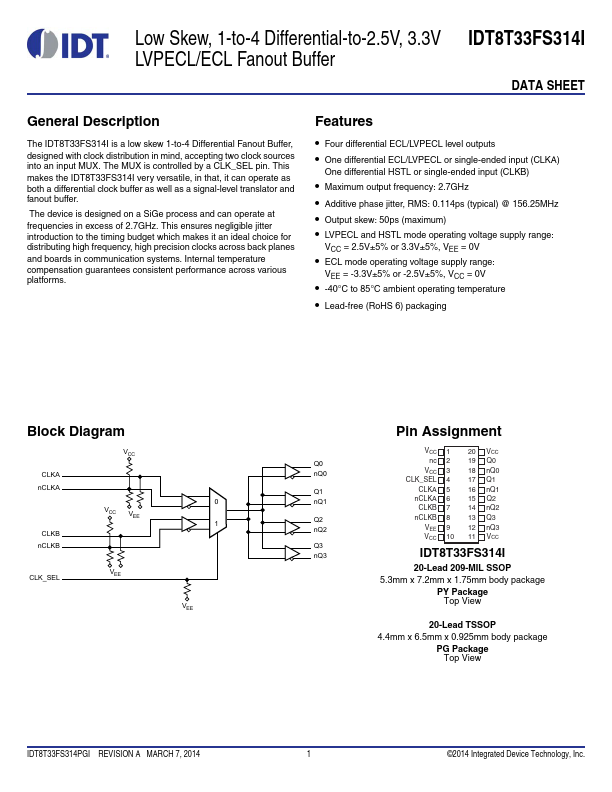

The IDT8T33FS314I is a low skew 1-to-4 Differential Fanout Buffer, designed with clock distribution in mind, accepting two clock sources into an input MUX. The MUX is controlled by a CLK_SEL pin.

- Four differential ECL/LVPECL level outputs

- One differential ECL/LVPECL or single-ended input (CLKA) One differential