IDT79R3041

Overview

- Instruction set compatible with IDT79R3000A and RISController Family MIPS RISC CPUs

- High level of integration minimizes system cost - RISC CPU - Multiply/divide unit - Instruction Cache - Data Cache - Programmable bus interface - Programmable port width support

- On-chip instruction and data caches - 2KB of Instruction Cache - 512B of Data Cache

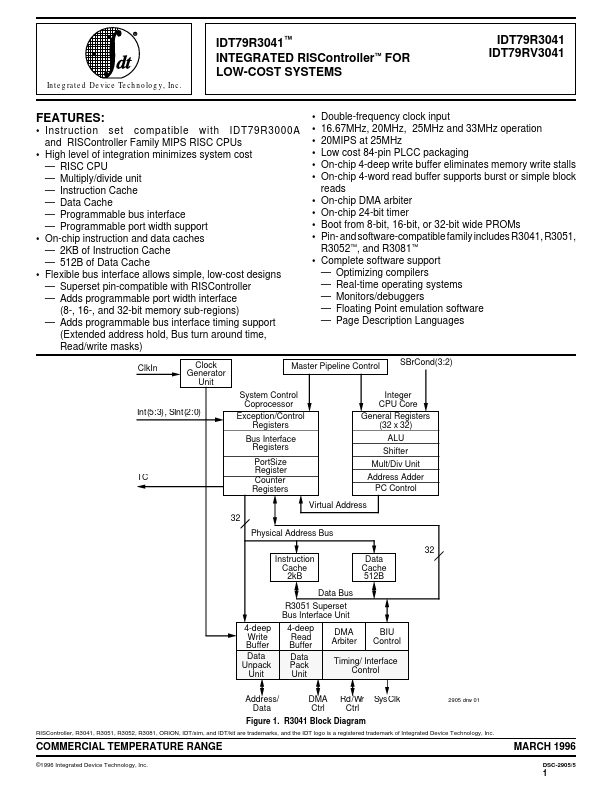

- Flexible bus interface allows simple, low-cost designs - Superset pin-compatible with RISController - Adds programmable port width interface (8-, 16-, and 32-bit memory sub-regions) - Adds programmable bus interface timing support (Extended address hold, Bus turn around time, Read/write masks) ClkIn Clock Generator Unit * * * * * * * * * *

- Double-frequency clock input 16.67MHz, 20MHz, 25MHz and 33MHz operation 20MIPS at 25MHz Low cost 84-pin PLCC packaging On-chip 4-deep write buffer eliminates memory write stalls On-chip 4-word read buffer supports burst or simple block reads On-chip DMA arbiter On-chip 24-bit timer Boot from 8-bit, 16-bit, or 32-bit wide PROMs Pin- and software-compatible family includes R3041, R3051, R3052™, and R3081™ Complete software support - Optimizing compilers - Real-time operating systems - Monitors/debuggers - Floating Point emulation software - Page Description Languages Master Pipeline Control System Control Coprocessor Exception/Control Registers Bus Interface Registers PortSize Register Counter Registers 32 Physical Address Bus SBrCond(3:2) Int(5:3), SInt(2:0) TC Integer CPU Core General Registers (32 x 32) ALU Shifter Mult/Div Unit Address Adder PC Control Virtual Address 32 Instruction Cache 2kB Data Bus R3051 Superset Bus Interface Unit 4-deep Write Buffer Data Unpack Unit Address/ Data 4-deep Read Buffer Data Pack Unit DMA Ctrl DMA Arbiter BIU Control Data Cache 512B Timing/ I