IS41C4100

IS41C4100 is 1Meg x 4 DYNAMIC RAM WITH EDO PAGE MODE manufactured by ISSI.

- Part of the IS41LV4100 comparator family.

- Part of the IS41LV4100 comparator family.

IS41C4100 IS41LV4100

1Meg x 4 (4-MBIT) DYNAMIC RAM WITH EDO PAGE MODE

Features

- TTL patible inputs and outputs

- Refresh Interval: 1024 cycles/16 ms

- Refresh Mode : RAS-Only, CAS-before-RAS (CBR), and Hidden

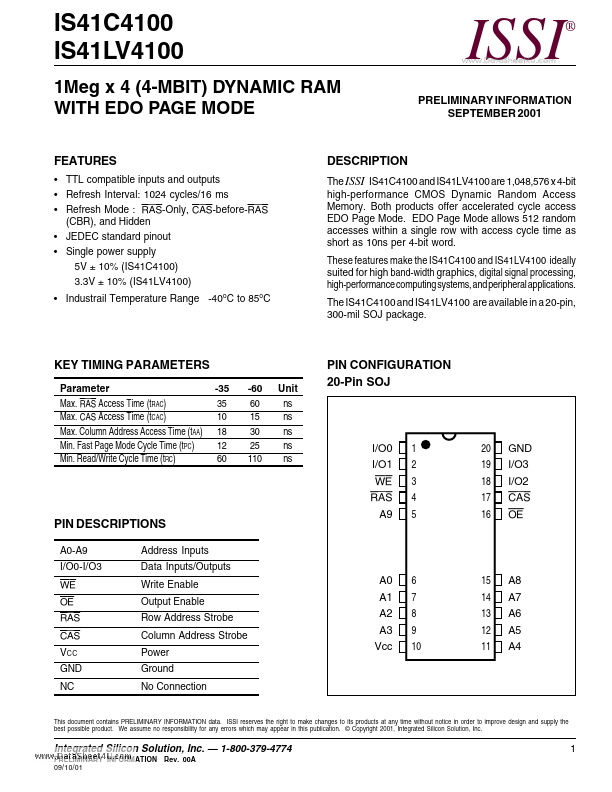

- JEDEC standard pinout

- Single power supply 5V ± 10% (IS41C4100) 3.3V ± 10% (IS41LV4100)

- Industrail Temperature Range -40oC to 85oC

..

ISSI

®

PRELIMINARY INFORMATION SEPTEMBER 2001

DESCRIPTION

The ISSI IS41C4100 and IS41LV4100 are 1,048,576 x 4-bit high-performance CMOS Dynamic Random Access Memory. Both products offer accelerated cycle access EDO Page Mode. EDO Page Mode allows 512 random accesses within a single row with access cycle time as short as...