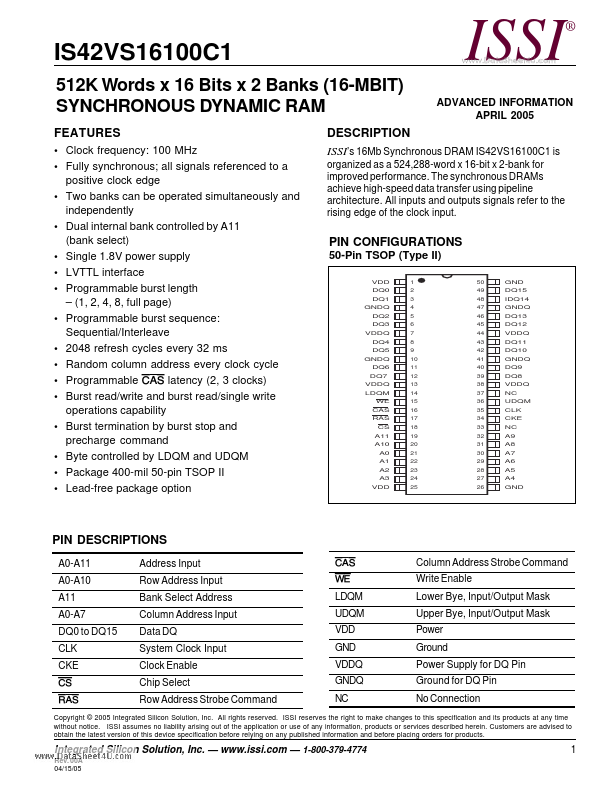

IS42VS16100C1

Description

ISSI’s 16Mb Synchronous DRAM IS42VS16100C1 is organized as a 524,288-word x 16-bit x 2-bank for improved performance.

Key Features

- Clock frequency: 100 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Two banks can be operated simultaneously and independently

- Dual internal bank controlled by A11 (bank select)

- Single 1.8V power supply

- LVTTL interface

- Programmable burst length – (1, 2, 4, 8, full page)

- Programmable burst sequence: Sequential/Interleave

- 2048 refresh cycles every 32 ms

- Random column address every clock cycle