IS43R86400D Description

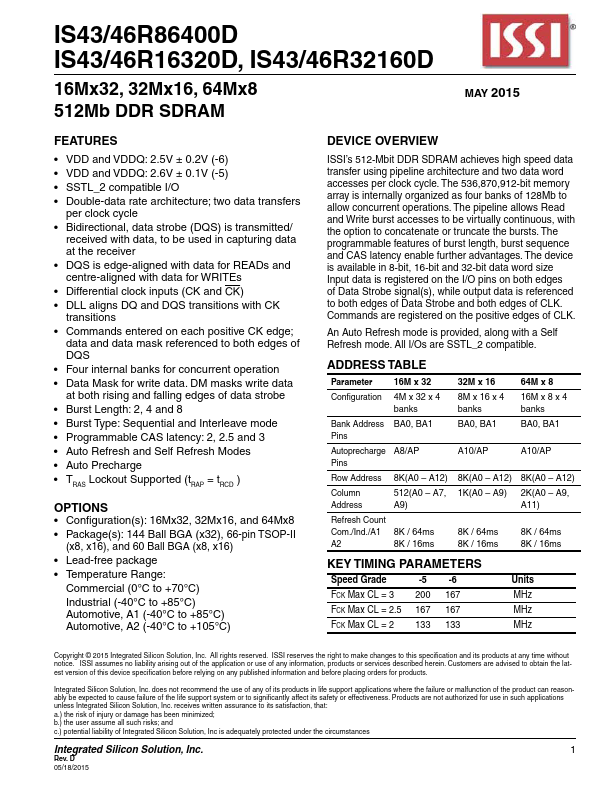

IS43/46R86400D IS43/46R16320D, IS43/46R32160D NOVEMBER 2012 16Mx32, 32Mx16, 64Mx8 512Mb DDR SDRAM.

IS43R86400D Key Features

- A12) 512(A0

- A7, A9)

- A12) 8K(A0

- A12) 1K(A0

- A9) 2K(A0

- A9, A11) 8K / 64ms 8K / 16ms

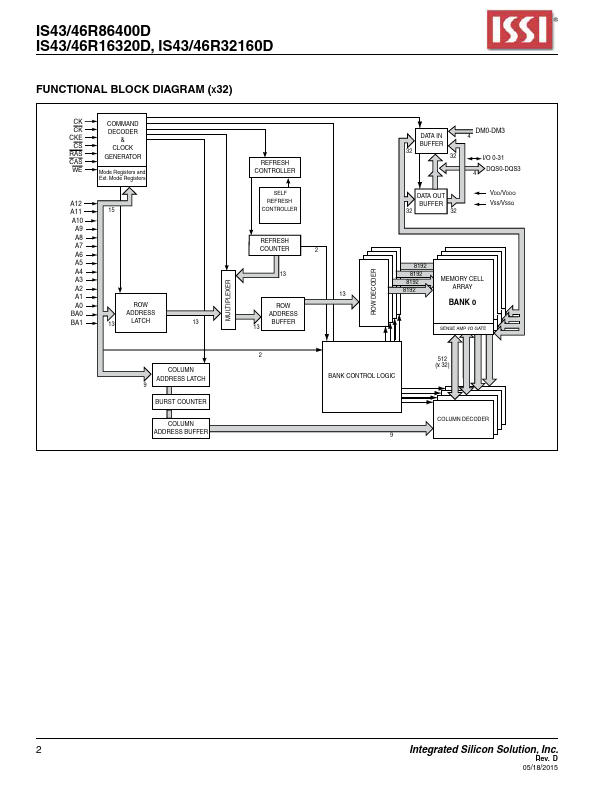

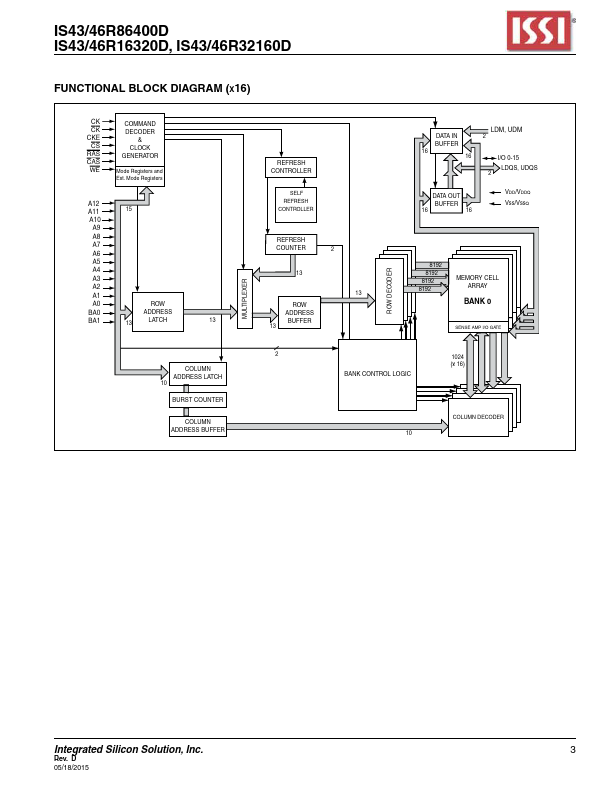

- Configuration(s): 16Mx32, 32Mx16, and 64Mx8

- Lead-free package