IS61NVVP409618B Description

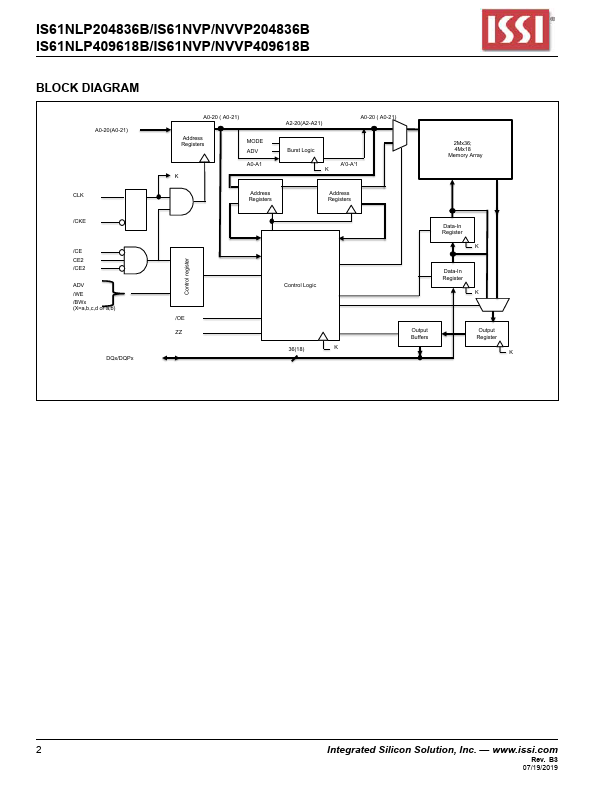

The 72 Meg product family.

IS61NVVP409618B Key Features

- 100 percent bus utilization

- No wait cycles between Read and Write

- Internal self-timed write cycle

- Individual Byte Write Control

- Single R/W (Read/Write) control pin

- Clock controlled, registered address

- Interleaved or linear burst sequence control us

- Three chip enables for simple depth expansion

- Power Down mode

- mon data inputs and data outputs