82C288

82C288 is BUS CONTROLLER manufactured by Intel Corporation.

Description

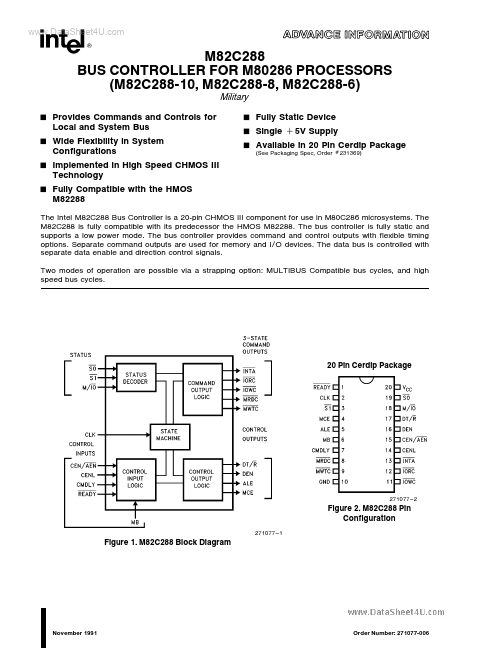

The following pin function descriptions are for the M82C288 bus controller Symbol Type CLK I Name and Function SYSTEM CLOCK provides the basic timing control for the M82C288 in an M80286 microsystem Its frequency is twice the internal processor clock frequency The falling edge of this input signal establishes when inputs are sampled and mand and control outputs change BUS CYCLE STATUS starts a bus cycle and along with M IO defines the type of bus cycle These inputs are active LOW A bus cycle is started when either S1 or S0 is sampled LOW at the falling edge of CLK Setup and hold times must be met for proper operation M80286 Bus Cycle Status Definition M IO 0 0 0 0 1 1 1 1 M IO I S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Interrupt Acknowledge I O Read I O Write None Idle Halt or Shutdown Memory Read Memory Write None Idle Type of Bus Cycle

S0 S1

MEMORY OR I O SELECT determines whether the current bus cycle is in the memory space or I O space When LOW the current bus cycle is in the I O space Setup and hold times must be met for proper operation MULTIBUS MODE SELECT determines timing of the mand and control outputs When HIGH the bus controller operates with MULTIBUS I patible timings When LOW the bus controller optimizes the mand and control output timing for short bus cycles The function of the CEN AEN input pin is selected by this signal This input is typically a strapping option and not dynamically changed MAND ENABLE LATCHED is a bus controller select signal which enables the bus controller to resopnd to the current bus cycle being initiated CENL is an active HIGH input latched internally at the end of each TS cycle CENL is used to select the appropriate bus controller for each bus cycle in a system where the CPU has more than one bus it can use...