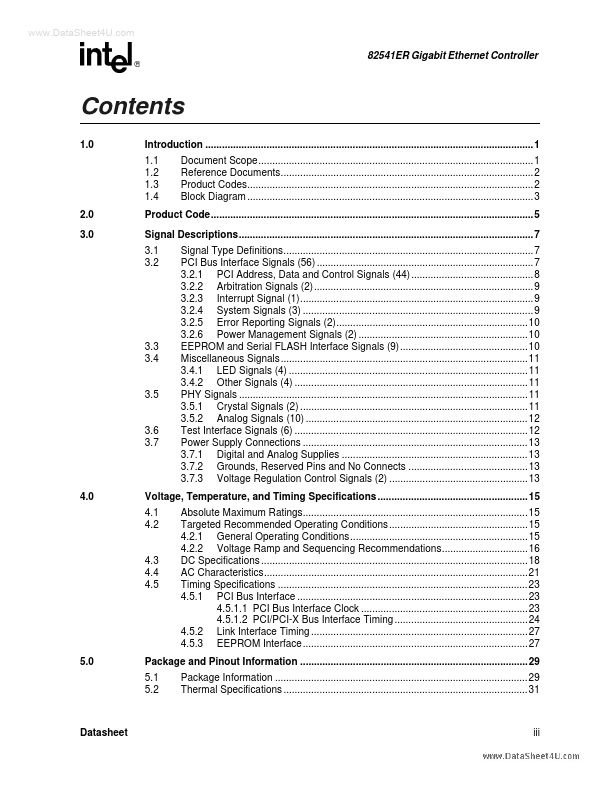

LU82541ER Key Features

- PCI revision 2.3, 32-bit, 33/66 MHz

- Algorithms that optimally use advanced PCI, MWI, MRM, and MRL mands

- 3.3 V (5 V tolerant PCI signaling) MAC Specific

- Low-latency transmit and receive queues

- IEEE 802.3x-pliant flow-control support with software-controllable thresholds

- Caches up to 64 packet descriptors in a single burst

- Programmable host memory receive buffers (256 B to 16 KB) and cache line size (16 B to 256 B)

- Wide, optimized internal data path architecture

- 64 KB configurable Transmit and Receive FIFO buffers PHY Specific

- Integrated for 10/100/1000 Mb/s operation