Datasheet Summary

UPI-C42 UPI-L42 UNIVERSAL PERIPHERAL INTERFACE CHMOS 8-BIT SLAVE MICROCONTROLLER

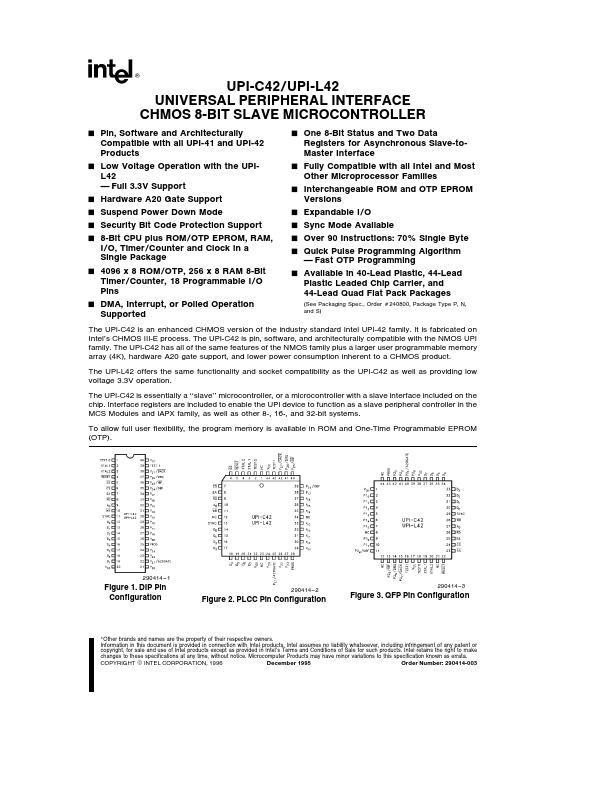

Pin Software and Architecturally patible with all UPI-41 and UPI-42 Products Low Voltage Operation with the UPIL42 Full 3 3V Support Hardware A20 Gate Support Suspend Power Down Mode Security Bit Code Protection Support 8-Bit CPU plus ROM OTP EPROM RAM I O Timer Counter and Clock in a Single Package 4096 x 8 ROM OTP 256 x 8 RAM 8-Bit Timer Counter 18 Programmable I O Pins DMA Interrupt or Polled Operation Supported

One 8-Bit Status and Two Data Registers for Asynchronous Slave-toMaster Interface Fully patible with all Intel and Most Other Microprocessor Families...