MS28F016SV

MS28F016SV is 16-Mbit FlashFileTM MEMORY manufactured by Intel.

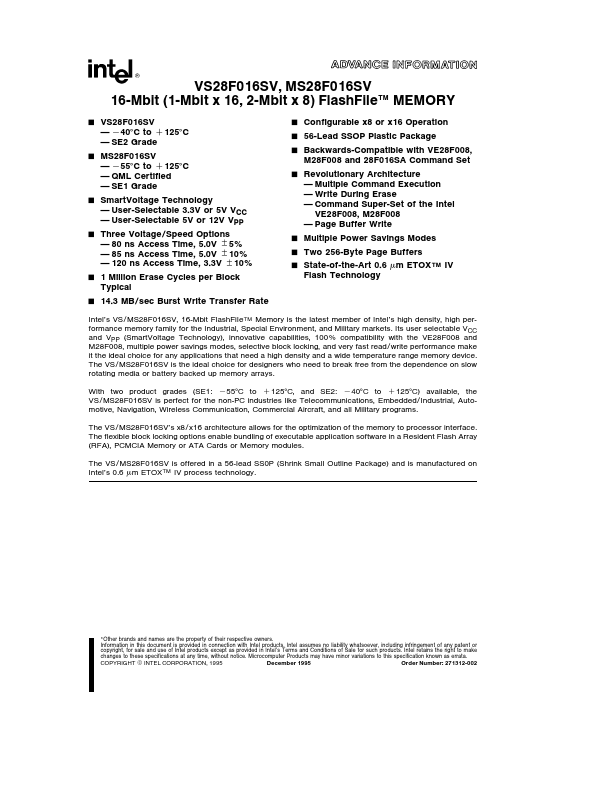

VS28F016SV MS28F016SV 16-Mbit (1-Mbit x 16 2-Mbit x 8) FlashFile TM MEMORY

VS28F016SV b 40 C to a 125 C SE2 Grade MS28F016SV b 55 C to a 125 C QML Certified SE1 Grade SmartVoltage Technology User-Selectable 3 3V or 5V VCC User-Selectable 5V or 12V VPP Three Voltage Speed Options 80 ns Access Time 5 0V g 5% 85 ns Access Time 5 0V g 10% 120 ns Access Time 3 3V g 10% 1 Million Erase Cycles per Block Typical 14 3 MB sec Burst Write Transfer Rate

Configurable x8 or x16 Operation 56-Lead SSOP Plastic Package Backwards-patible with VE28F008 M28F008 and 28F016SA mand Set Revolutionary Architecture Multiple mand Execution Write During Erase mand Super-Set of the Intel...