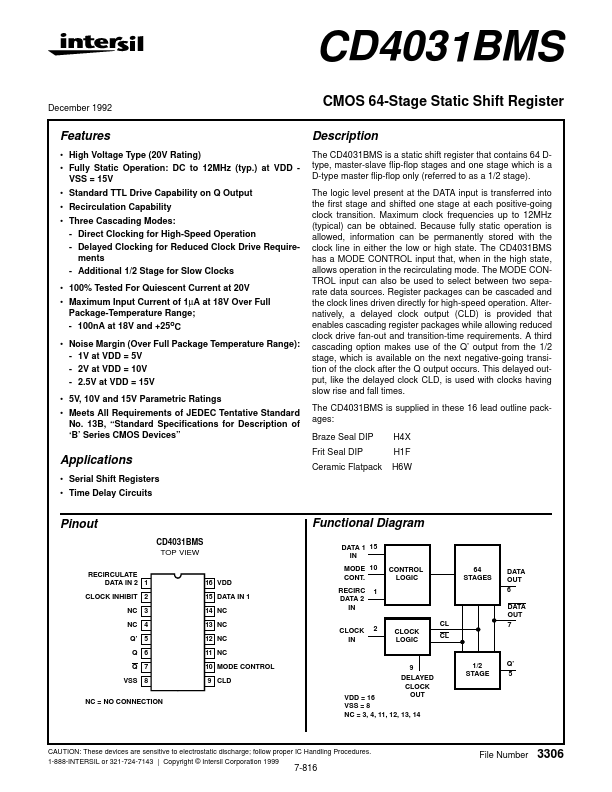

CD4031BMS

Overview

The CD4031BMS is a static shift register that contains 64 Dtype, master-slave flip-flop stages and one stage which is a D-type master flip-flop only (referred to as a 1/2 stage). The logic level present at the DATA input is transferred into the first stage and shifted one stage at each positive-going clock transition.

- High Voltage Type (20V Rating)

- Fully Static Operation: DC to 12MHz (typ.) at VDD VSS = 15V

- Standard TTL Drive Capability on Q Output

- Recirculation Capability

- Three Cascading Modes: - Direct Clocking for High-Speed Operation - Delayed Clocking for Reduced Clock Drive Requirements - Additional 1/2 Stage for Slow Clocks

- 100% Tested For Quiescent Current at 20V

- Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range; - 100nA at 18V and +25oC

- Noise Margin (Over Full Package Temperatur