HM-6561 Datasheet Text

HM-6561/883

March 1997

256 x 4 CMOS RAM

Description

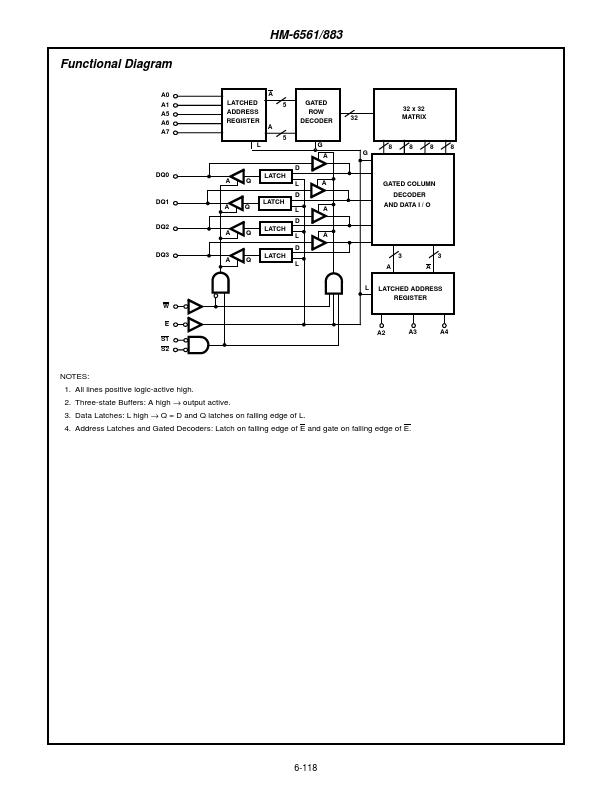

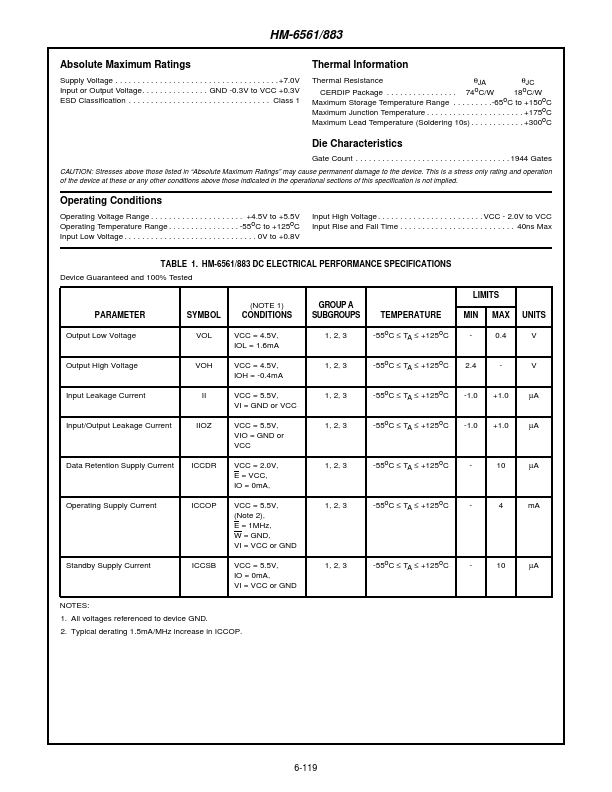

The HM-6561/883 is a 256 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation. On-chip latches are provided for address and data outputs allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays. The data inputs and outputs are multiplexed internally for mon I/O bus patibility. The HM-6561/883 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

Features

- This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Low Power Standby

- -

- - 50µW Max

- Low Power Operation

- - . . . 20mW/MHz Max

- Fast Access Time-

- -

- . . 200ns Max

- Data Retention

- -

- - . . . .at 2.0V Min

- TTL patible Input/Output

- High Output Drive

- 1 TTL Load

- On-Chip Address Registers

- mon Data In/Out

- Three-State Output

- Easy Microprocessor Interfacing

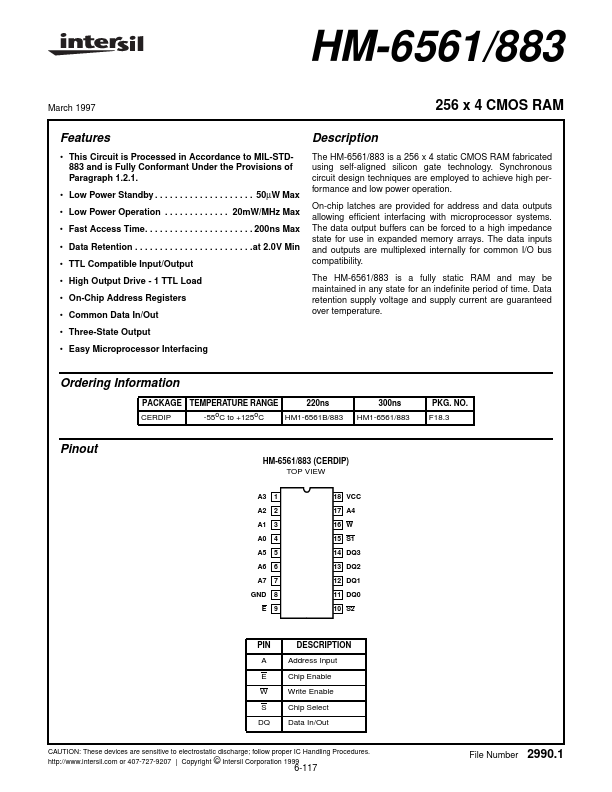

Ordering Information

PACKAGE TEMPERATURE RANGE CERDIP -55oC to +125oC 220ns HM1-6561B/883 300ns HM1-6561/883 PKG. NO. F18.3

Pinout

HM-6561/883 (CERDIP) TOP VIEW

A3 A2 A1 A0 A5 A6 A7 GND E 1 2 3 4 5 6 7 8 9 18 VCC 17 A4 16 W 15 S1 14 DQ3 13 DQ2 12 DQ1 11 DQ0 10 S2...