HMA510883

Description

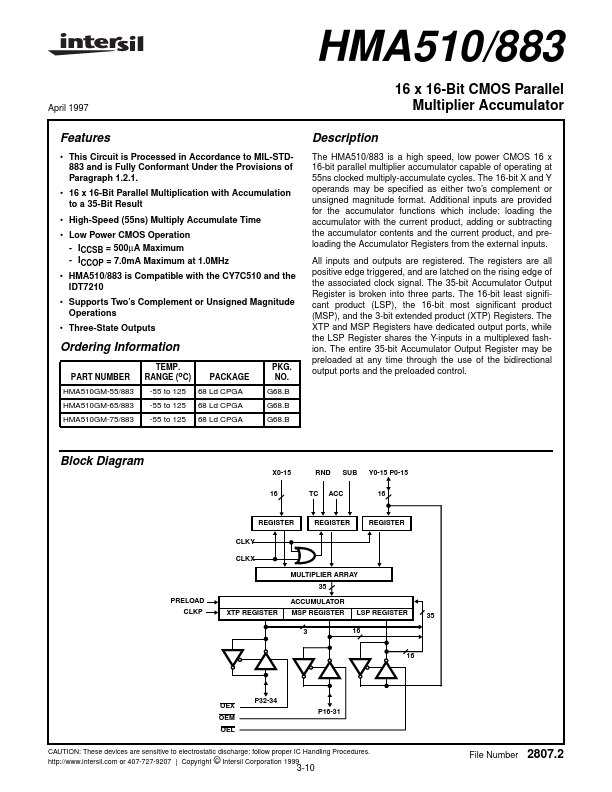

The HMA510/883 is a high speed, low power CMOS 16 x 16-bit parallel multiplier accumulator capable of operating at 55ns clocked multiply-accumulate cycles. The 16-bit X and Y operands may be specified as either two’s plement or unsigned magnitude format.

Key Features

- This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1

- 16 x 16-Bit Parallel Multiplication with Accumulation to a 35-Bit Result

- High-Speed (55ns) Multiply Accumulate Time

- Low Power CMOS Operation

- ICCSB = 500µA Maximum

- ICCOP = 7.0mA Maximum at 1.0MHz

- Supports Two’s plement or Unsigned Magnitude Operations

- Three-State Outputs