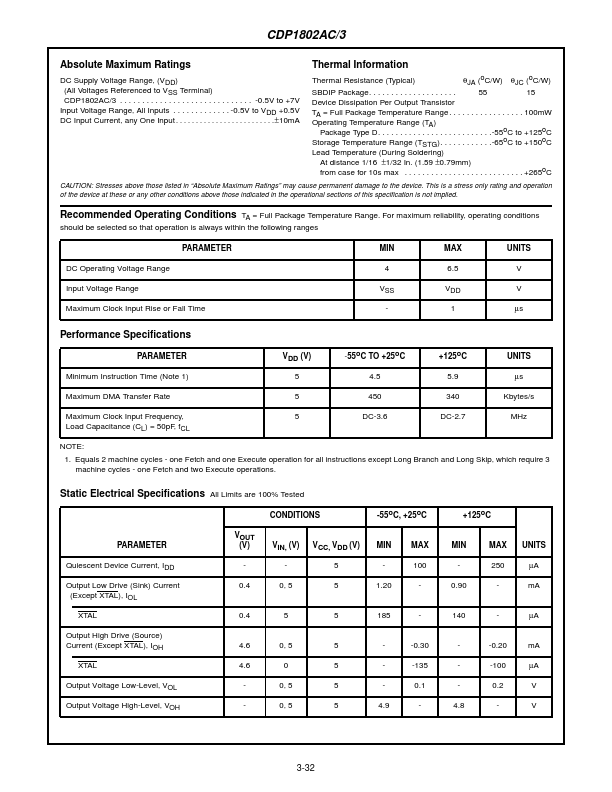

Datasheet Summary

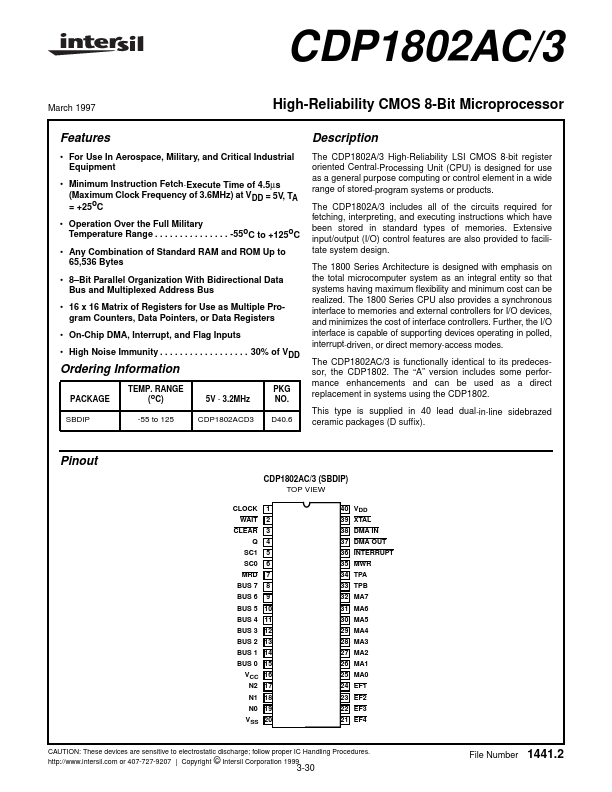

CDP1802AC/3

March 1997

High-Reliability CMOS 8-Bit Microprocessor

Description

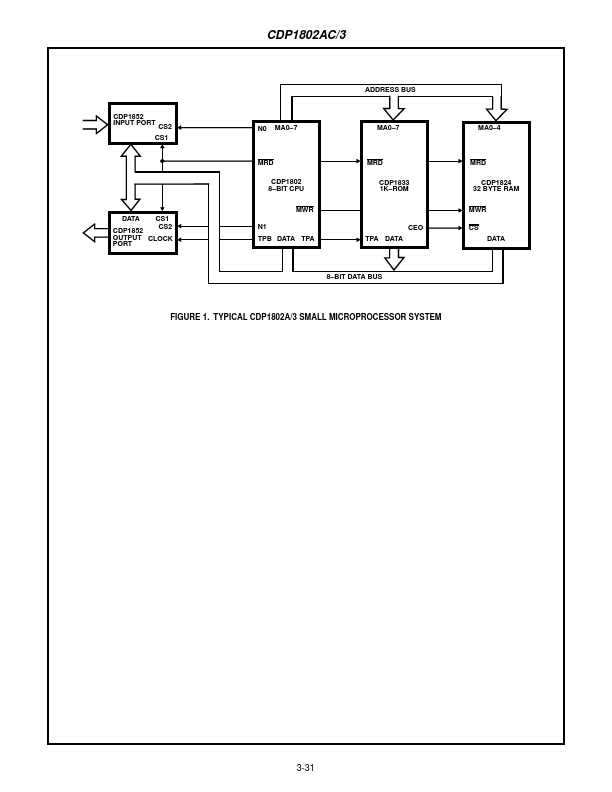

The CDP1802A/3 High-Reliability LSI CMOS 8-bit register oriented Central-Processing Unit (CPU) is designed for use as a general purpose puting or control element in a wide range of stored-program systems or products. The CDP1802A/3 includes all of the circuits required for fetching, interpreting, and executing instructions which have been stored in standard types of memories. Extensive input/output (I/O) control Features are also provided to facilitate system design. The 1800 Series Architecture is designed with emphasis on the total microputer system as an integral entity so that systems having maximum...