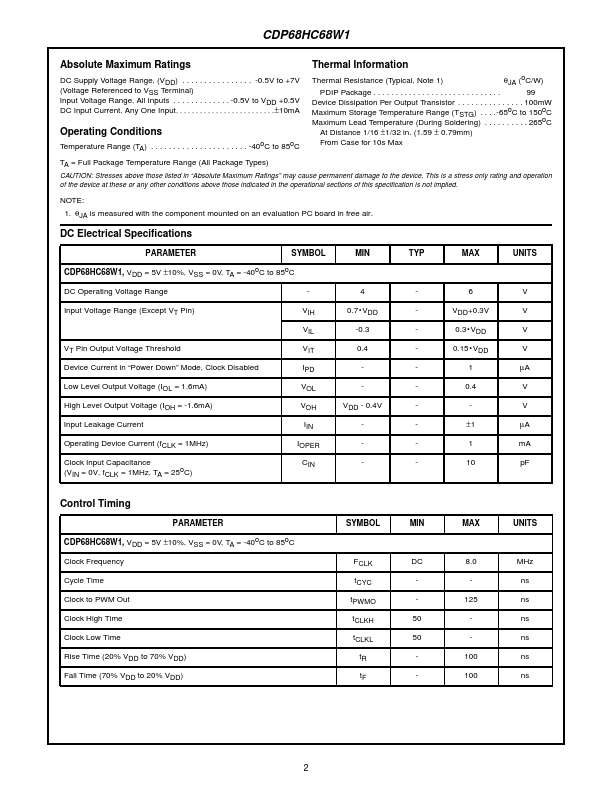

Datasheet Summary

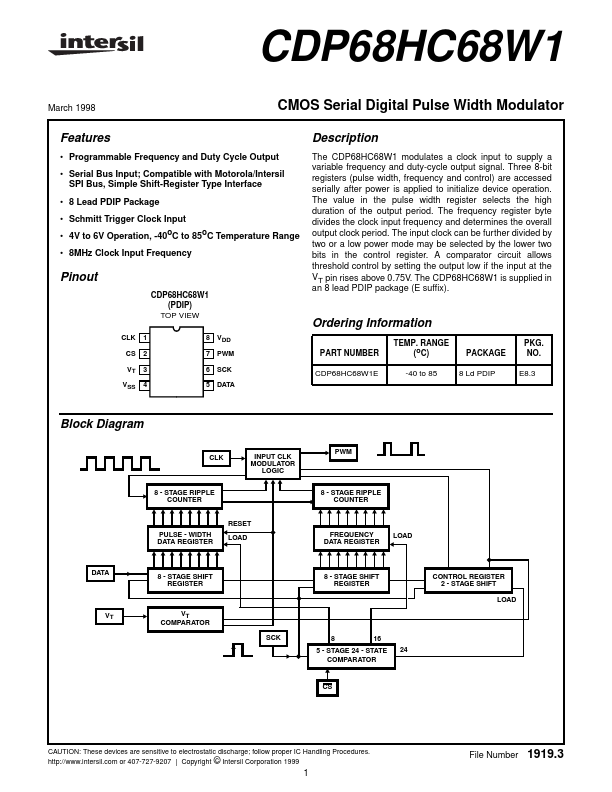

CDP68HC68W1

March 1998

CMOS Serial Digital Pulse Width Modulator

Description

The CDP68HC68W1 modulates a clock input to supply a variable frequency and duty-cycle output signal. Three 8-bit registers (pulse width, frequency and control) are accessed serially after power is applied to initialize device operation. The value in the pulse width register selects the high duration of the output period. The frequency register byte divides the clock input frequency and determines the overall output clock period. The input clock can be further divided by two or a low power mode may be selected by the lower two bits in the control register. A parator circuit allows threshold control by setting...