KKA8351

KKA8351 is DC-COUPLED VERTICAL DEFLECTION CIRCUIT manufactured by Kodenshi AUK Group.

FEATURES

- -

- -

- -

- - Few external ponents Highly efficient fully DC-coupled vertical output bridge circuit Vertical flyback switch Guard circuit Protection against:

- short-circuit of the output pins (7 and 4)

- short-circuit of the output pins to VP Temperature (thermal) protection High EMC immunity because of mon mode inputs A guard signal in zoom mode.

GENERAL DESCRIPTION

The KKA8351 is a power circuit for use in 90° and 110° colour deflection systems for field frequencies of 50 to 120 Hz. The circuit provides a DC driven vertical deflection output circuit, operating as a highly efficient class G system.

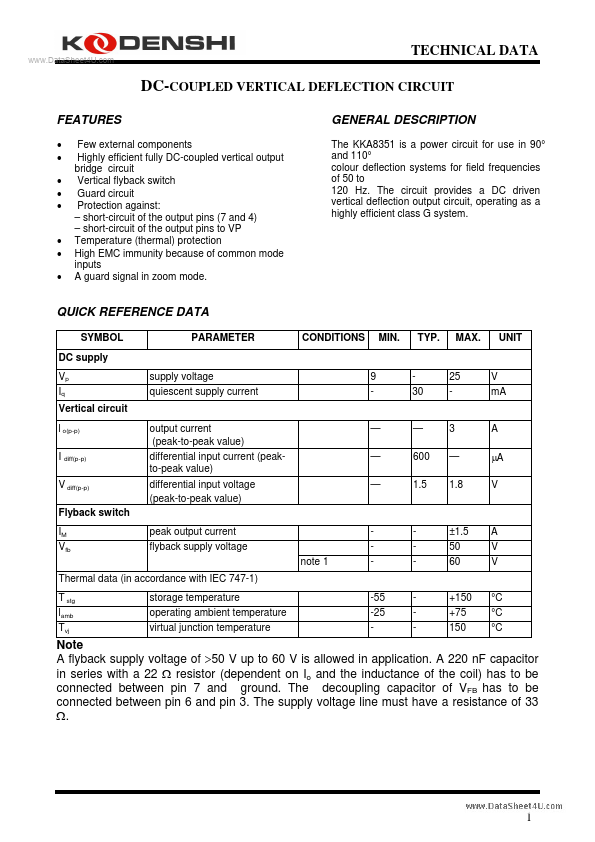

QUICK REFERENCE DATA

SYMBOL DC supply Vp Iq Vertical circuit l o(p-p) I diff(p-p) V diff(p-p) Flyback switch IM Vfb peak output current flyback supply voltage note 1 Thermal data (in accordance with IEC 747-1) T stg lamb Tvj storage temperature operating ambient temperature virtual junction temperature -55 -25 +150 +75 150 °C °C °C ±1.5 50 60 A V V output current (peak-to-peak value) differential input current (peakto-peak value) differential input voltage (peak-to-peak value)

- -

- - 600 1.5 3

- 1.8 A µA V supply voltage quiescent supply current 9 30 25 V m A PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Note A flyback supply voltage of >50 V up to 60 V is allowed in application. A 220 n F capacitor in series with a 22 Ω resistor (dependent on Io and the inductance of the coil) has to be connected between pin 7 and ground. The decoupling capacitor of VFB has to be connected between pin 6 and pin 3. The supply voltage line must have a resistance of 33 Ω.

..

BLOCK DIAGRAM.

VP VO(guard) VFB

3 +VP

CURRENT SOURCE

+VP 7 VO(A) +VO(A)

Idrive(pos)

-IS +IT -IT 9 VI(fb)

Idrive(neg)

2 +IS +v

+v P

4 VO(B) -VO(B)

5 GND

..

PINNING

SYMBOL I drive(pos) l drive(neg) Vp VO(B) GND Vfb Vo(a) Vo(guard) V|(fb) PIN 1 2 3 4 5 6 7 8 9 DESCRIPTION input power-stage (positive); includes li(sb) signal bias input power-stage (negative);...