ML620Q418A

ML620Q418A is Ultra Low Power 16-bit Microcontroller manufactured by LAPIS.

- Part of the ML620Q416A comparator family.

- Part of the ML620Q416A comparator family.

DESCRIPTION

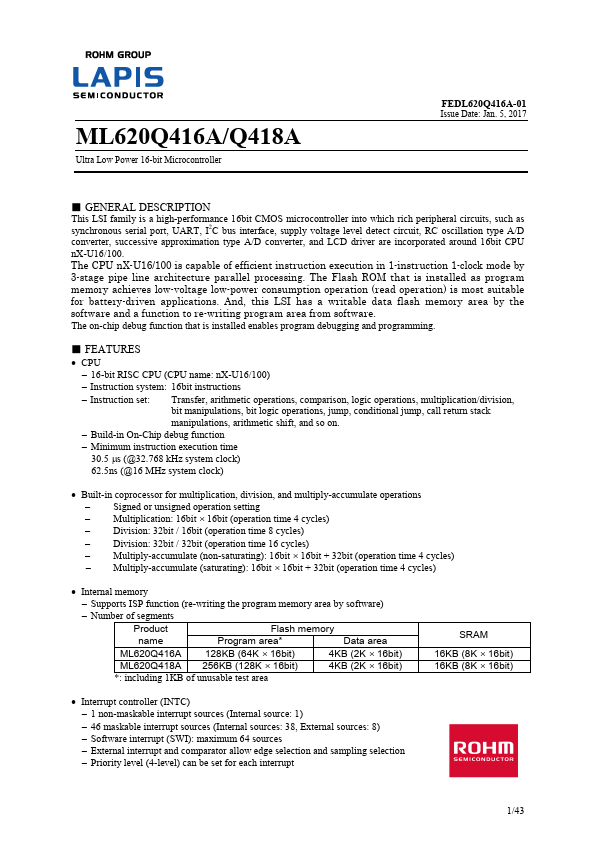

This LSI family is a high-performance 16bit CMOS microcontroller into which rich peripheral circuits, such as synchronous serial port, UART, I2C bus interface, supply voltage level detect circuit, RC oscillation type A/D converter, successive approximation type A/D converter, and LCD driver are incorporated around 16bit CPU n X-U16/100. The CPU n X-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by 3-stage pipe line architecture parallel processing. The Flash ROM that is installed as program memory achieves low-voltage low-power consumption operation (read operation) is most suitable for battery-driven applications. And, this LSI has a writable data flash memory area by the software and a function to re-writing program area from software. The on-chip debug function that is installed enables program debugging and programming.

- FEATURES

- CPU

- 16-bit RISC CPU (CPU name: n X-U16/100)

- Instruction system: 16bit instructions

- Instruction set: Transfer, arithmetic operations, parison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on.

- Build-in On-Chip debug function

- Minimum instruction execution time 30.5 µs (@32.768 k Hz system clock) 62.5ns (@16 MHz system clock)

- Built-in coprocessor for multiplication, division, and multiply-accumulate operations

- Signed or unsigned operation setting

- Multiplication: 16bit × 16bit (operation time 4 cycles)

- Division: 32bit / 16bit (operation time 8 cycles)

- Division: 32bit / 32bit (operation time 16 cycles)

- Multiply-accumulate (non-saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Multiply-accumulate (saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Internal memory

- Supports ISP function (re-writing the program memory area by software)

- Number of segments

Product

Flash memory name

Program area-

Data area

ML620Q416A...