24C32

Representative 24C32 image (package may vary by manufacturer)

Overview

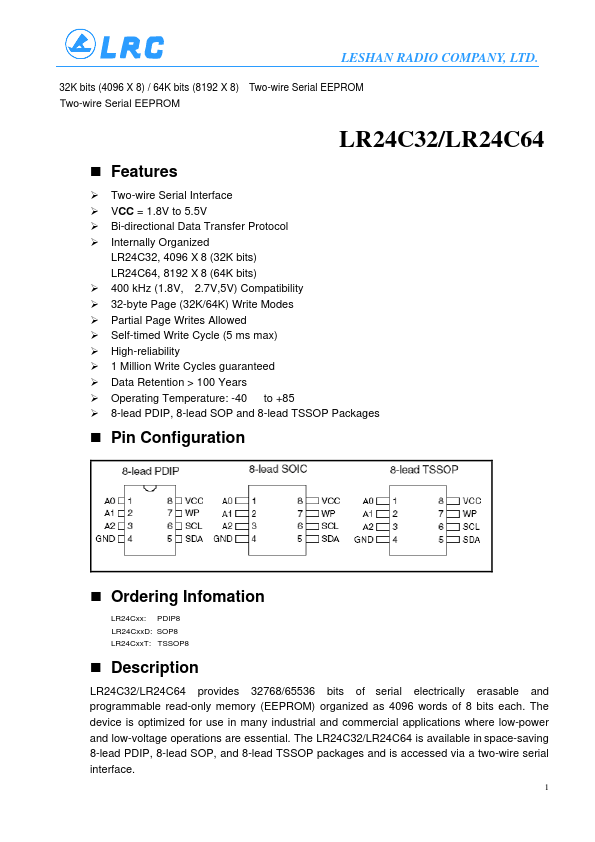

LR24C32/LR24C64 provides 32768/65536 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 4096 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential.