L74VHC1G125

L74VHC1G125 is Noninverting 3-State Buffer manufactured by LRC.

Features

- -

- -

- -

- High Speed: t PD = 3.5 ns (Typ) at VCC = 5.0 V Low Power Dissipation: ICC = 1 m A (Max) at TA = 25°C Power Down Protection Provided on Inputs Balanced Propagation Delays Pin and Function patible with Other Standard Logic Families Chip plexity: FETs = 58; Equivalent Gates = 15 Pb- Free Packages are Available

5 4

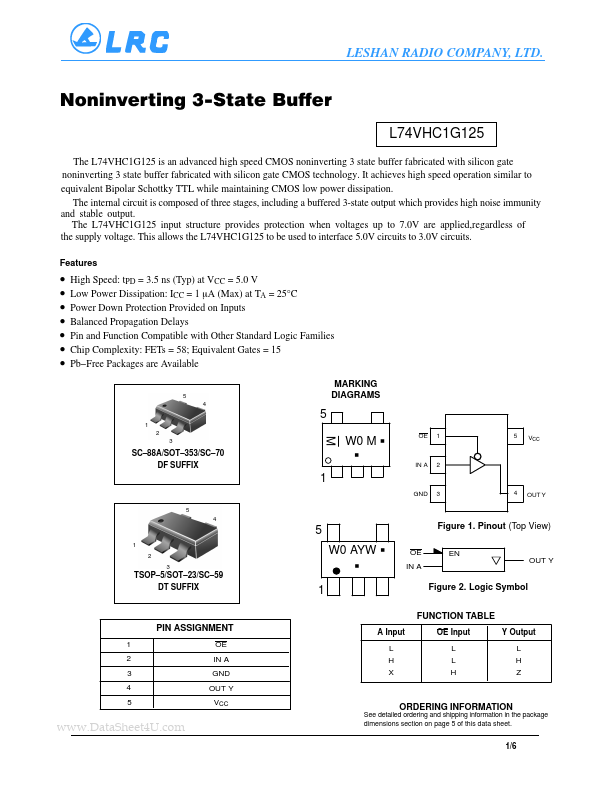

MARKING DIAGRAMS

1 2 3

SC- 88A/SOT- 353/SC- 70 DF SUFFIX

W0 M G G

5 4

M 5

IN A

OUT Y

Figure 1. Pinout (Top View)

1 2 3

TSOP- 5/SOT- 23/SC- 59 DT SUFFIX

W0 AYW G G 1

OE IN A

OUT Y

Figure 2. Logic Symbol FUNCTION TABLE

PIN ASSIGNMENT

1 2 3 4 5 OE IN A GND OUT Y VCC

A Input L H X

OE Input L L H

Y Output L H Z

ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

..

1/6

LESHAN RADIO PANY, LTD.

MAXIMUM RATINGS

Symbol VCC VIN VOUT IIK IOK IOUT ICC PD q JA TL TJ Tstg VESD DC Supply Voltage DC Input Voltage DC Output Voltage Input Diode Current Output Diode Current DC Output Current, per Pin DC Supply Current, VCC and GND Power Dissipation in Still Air Thermal Resistance Lead Temperature, 1 mm from Case for 10 s Junction Temperature Under Bias Storage Temperature ESD Withstand Voltage Human Body Model (Note 1) Machine Model (Note 2) Charged Device Model (Note 3) Above VCC and Below GND at 125°C (Note 4) SC- 88A, TSOP- 5 SC- 88A, TSOP- 5 VOUT < GND; VOUT > VCC VCC = 0 High or Low State Characteristics Value

- 0.5 to...