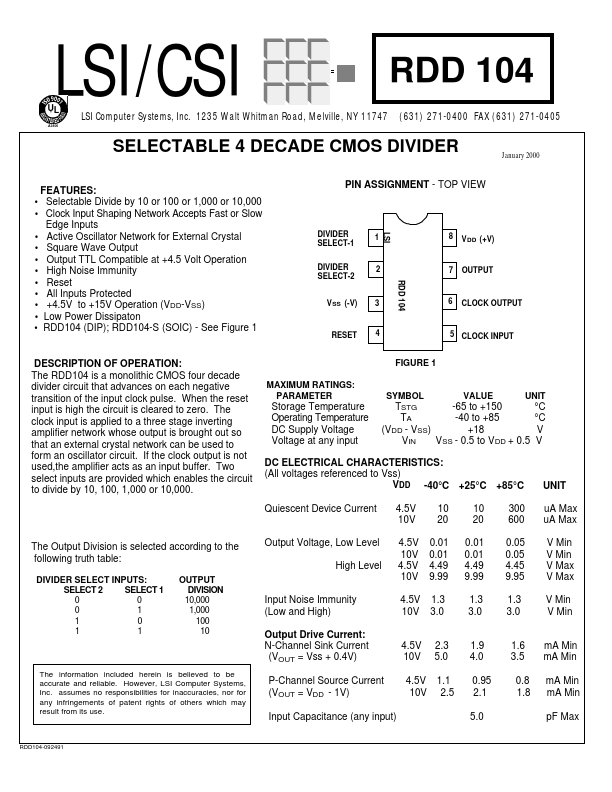

RDD104 Description

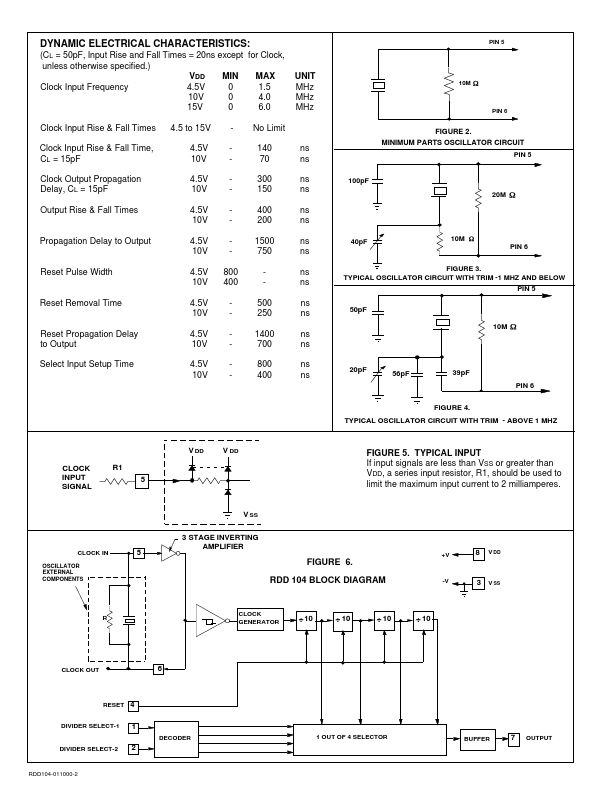

The RDD104 is a monolithic CMOS four decade divider circuit that advances on each negative transition of the input clock pulse. When the reset input is high the circuit is cleared to zero. The clock input is applied to a three stage inverting amplifier network whose output is brought out so that an external crystal network can be used to form an oscillator circuit.

RDD104 Key Features

- Selectable Divide by 10 or 100 or 1,000 or 10,000

- Clock Input Shaping Network Accepts Fast or Slow Edge Inputs

- Active Oscillator Network for External Crystal

- Square Wave Output

- Output TTL patible at +4.5 Volt Operation

- High Noise Immunity

- All Inputs Protected

- +4.5V to +15V Operation (VDD-VSS)

- Low Power Dissipaton

- RDD104 (DIP); RDD104-S (SOIC)