GAL20XV10

Overview

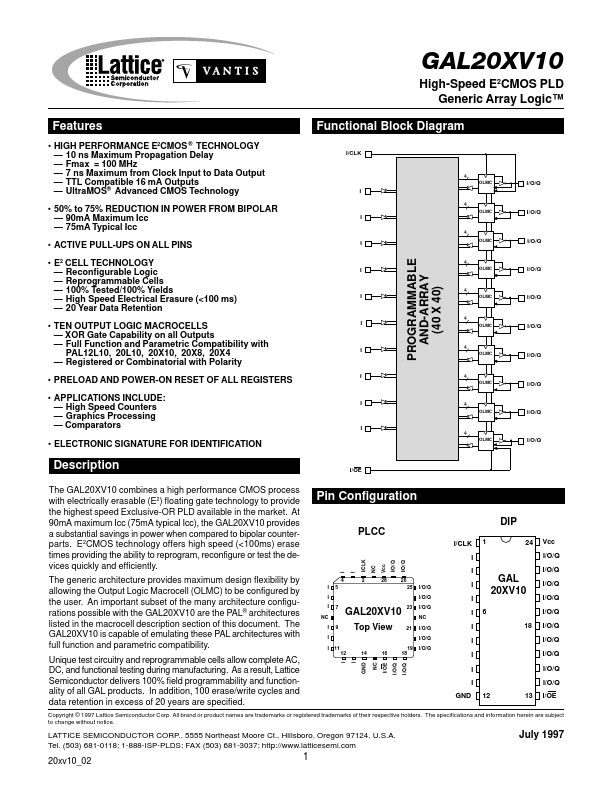

The GAL20XV10 combines a high performance CMOS process with electrically erasable (E2) floating gate technology to provide the highest speed Exclusive-OR PLD available in the market. At 90mA maximum Icc (75mA typical Icc), the GAL20XV10 provides a substantial savings in power when compared to bipolar counterparts.

- HIGH PERFORMANCE E2CMOS ® TECHNOLOGY - 10 ns Maximum Propagation Delay - Fmax = 100 MHz - 7 ns Maximum from Clock Input to Data Output - TTL Compatible 16 mA Outputs - UltraMOS® Advanced CMOS Technology

- 50% to 75% REDUCTION IN POWER FROM BIPOLAR - 90mA Maximum Icc - 75mA Typical Icc

- ACTIVE PULL-UPS ON ALL PINS

- E2 CELL TECHNOLOGY - Reconfigurable Logic - Reprogrammable Cells - 100% Tested/100% Yields - High Speed Electrical Erasure (<100 ms) - 20 Year Data Retention

- TEN OUTPUT LOGIC MACROCELLS - XOR Gate Capability on all Outputs - Full Function and Parametric Compatibility with PAL12L10, 20L10, 20X10, 20X8, 20X4 - Registered or Combinatorial with Polarity

- PRELOAD AND POWER-ON RESET OF ALL REGISTERS