ISPCLOCK5500

ISPCLOCK5500 is In-System Programmable Zero-Delay manufactured by Lattice Semiconductor.

- Part of the ISPCLOCK5300S comparator family.

- Part of the ISPCLOCK5300S comparator family.

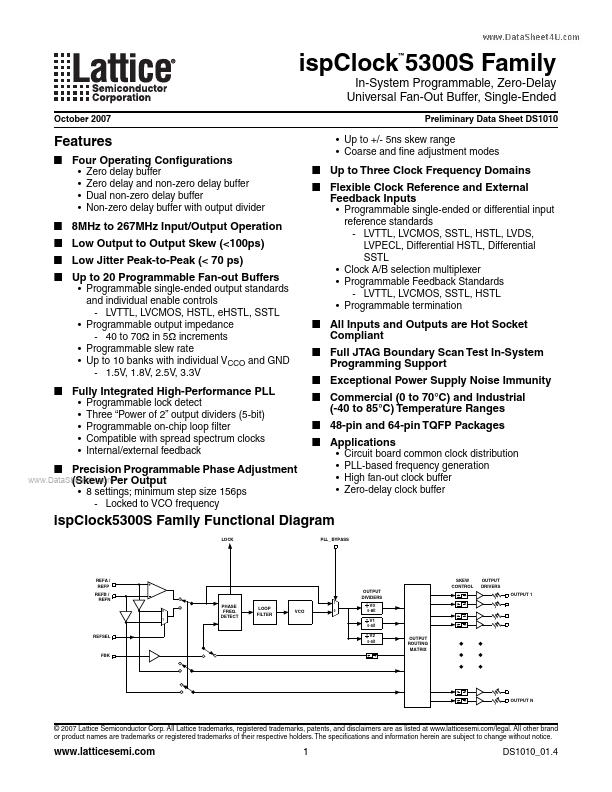

ispClock 5300S Family

™

In-System Programmable, Zero-Delay Universal Fan-Out Buffer, Single-Ended

October 2007 Preliminary Data Sheet DS1010

Features

- Four Operating Configurations

- -

- - Zero delay buffer Zero delay and non-zero delay buffer Dual non-zero delay buffer Non-zero delay buffer with output divider

- Up to +/- 5ns skew range

- Coarse and fine adjustment modes

- Up to Three Clock Frequency Domains

- Flexible Clock Reference and External Feedback Inputs

- Programmable single-ended or differential input reference standards

- LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL, Differential HSTL, Differential SSTL

- Clock A/B selection multiplexer

- Programmable Feedback Standards

- LVTTL,...