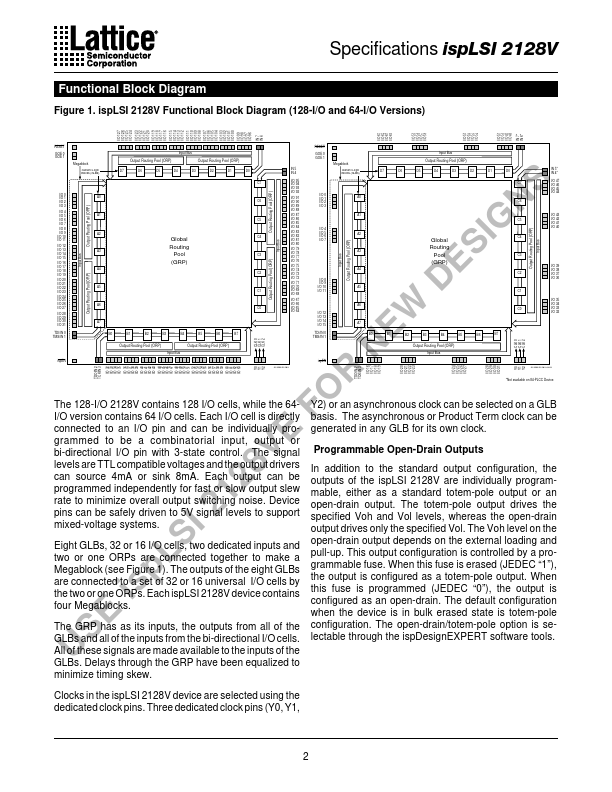

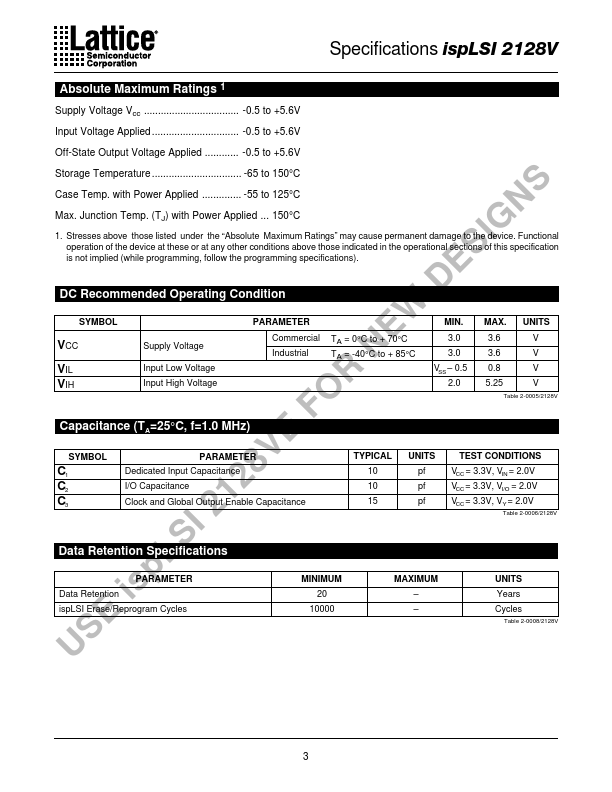

Datasheet Summary

ispLSI 2128V

3.3V High Density Programmable Logic Features

- HIGH DENSITY PROGRAMMABLE LOGIC

- -

- -

- 6000 PLD Gates 128 and 64 I/O Pin Versions, Eight Dedicated Inputs 128 Registers High Speed Global Interconnect Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

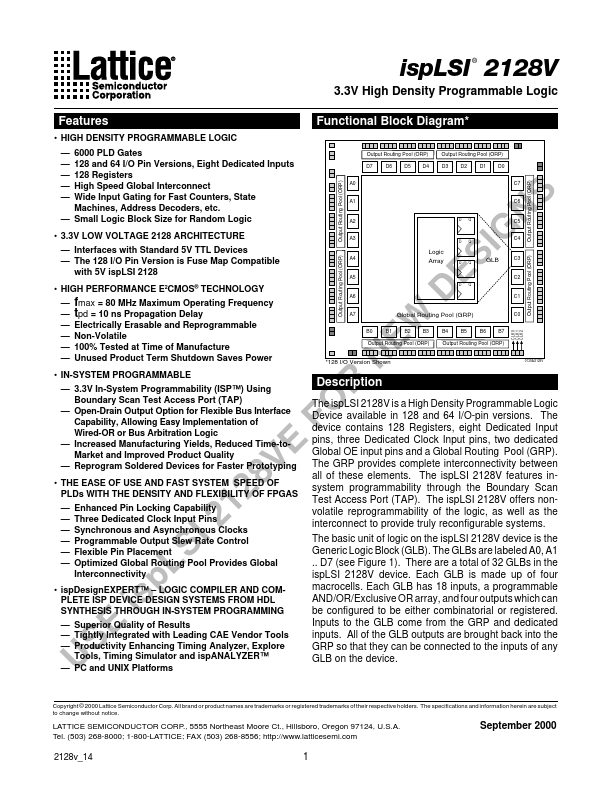

Output Routing Pool (ORP) D7 D6 D5 D4 Output Routing Pool (ORP) D3 D2 D1 D0 C7

®

Functional Block Diagram-

Output Routing Pool (ORP)

A0

A1

C6

A2

- 3.3V LOW VOLTAGE 2128 ARCHITECTURE

- Interfaces with Standard 5V TTL Devices

- The 128 I/O Pin Version is Fuse Map patible with 5V ispLSI 2128

- HIGH PERFORMANCE E CMOS TECHNOLOGY

- -

- -

- -

2 ®

A3

Output...