ISPXPLD5768MX

ISPXPLD5768MX is eXpanded Programmable Logic Device XPLD manufactured by Lattice Semiconductor.

- Part of the ISPXPLD5000MX comparator family.

- Part of the ISPXPLD5000MX comparator family.

DISSECLOENCTTINDUEEVIDCES isp XPLDTM 5000MX Family

3.3V, 2.5V and 1.8V In-System Programmable e Xpanded Programmable Logic Device XPLD™ Family

February 2010

Data Sheet

Features

- Flexible Multi-Function Block (MFB) Architecture

- Super WIDE™ logic (up to 136 inputs)

- Arithmetic capability

- Single- or Dual-port SRAM

- FIFO

- Ternary CAM

- sys CLOCK™ PLL Timing Control

- Multiply and divide between 1 and 32

- Clock shifting capability

- External feedback capability

- sys IO™ Interfaces

- LVCMOS 1.8, 2.5, 3.3V

- Programmable impedance

- Hot-socketing

- Flexible bus-maintenance (Pull-up, pulldown, bus-keeper, or none)

- Open drain operation

- SSTL 2, 3 (I & II)

- HSTL (I, III, IV)

- PCI 3.3

- GTL+

- LVDS

- LVPECL

- LVTTL

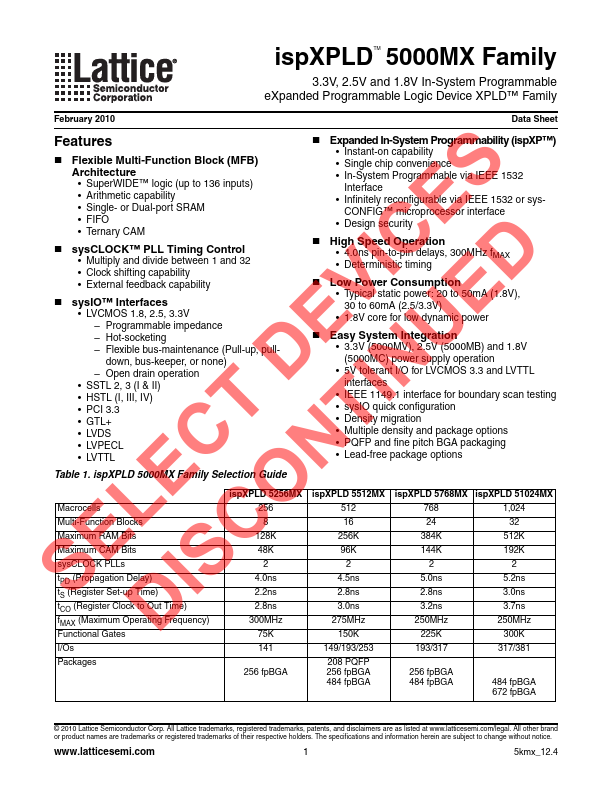

Table 1. isp XPLD 5000MX Family Selection Guide

- Expanded In-System Programmability (isp...