ispGDX160VA-3B208 Description

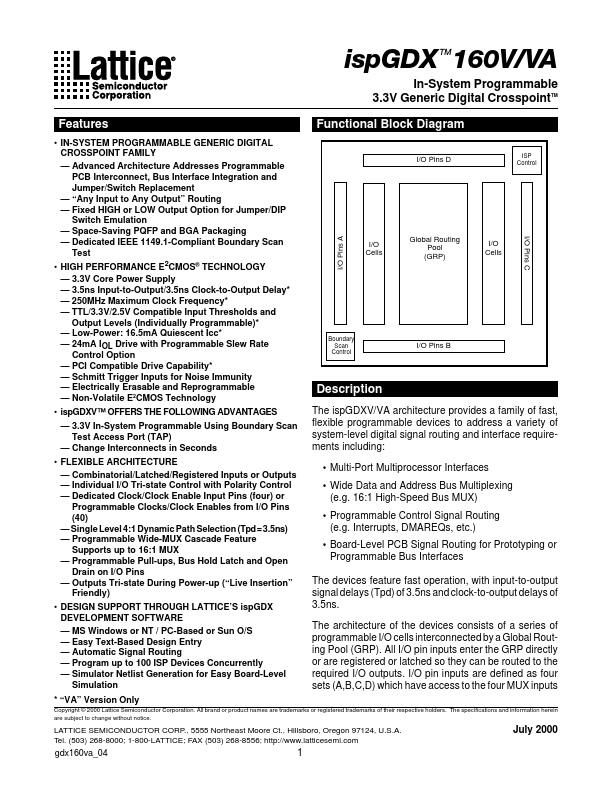

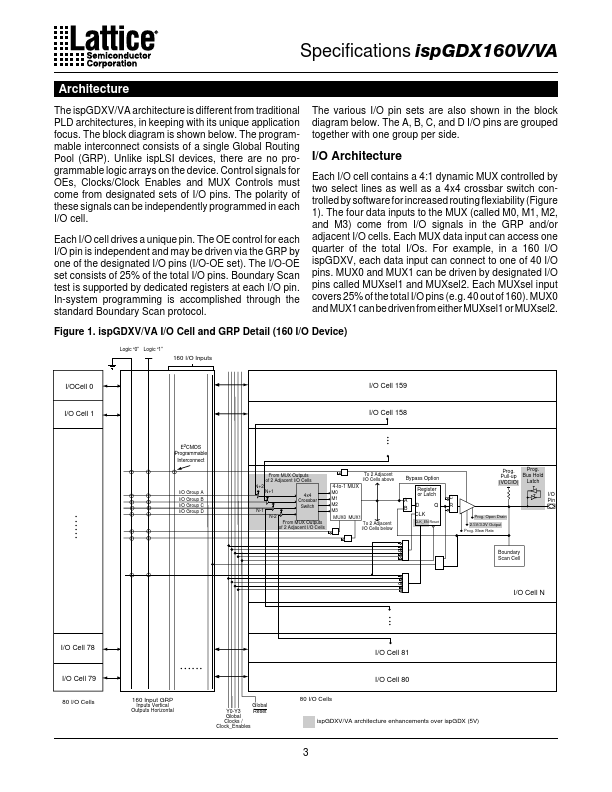

The ispGDXV/VA architecture provides a family of fast, flexible programmable devices to address a variety of system-level digital signal routing and interface requirements including: Multi-Port Multiprocessor Interfaces Wide Data and Address Bus Multiplexing (e.g. 16:1 High-Speed Bus MUX) Programmable Control Signal Routing (e.g.

ispGDX160VA-3B208 Key Features

- IN-SYSTEM PROGRAMMABLE GENERIC DIGITAL CROSSPOINT FAMILY

- Advanced Architecture Addresses Programmable PCB Interconnect, Bus Interface Integration and Jumper/Switch Replacement

- Fixed HIGH or LOW Output Option for Jumper/DIP Switch Emulation

- Space-Saving PQFP and BGA Packaging

- Dedicated IEEE 1149.1-pliant Boundary Scan Test

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- 3.3V Core Power Supply

- 3.5ns Input-to-Output/3.5ns Clock-to-Output Delay

- 250MHz Maximum Clock Frequency