ispLSI1016EA Key Features

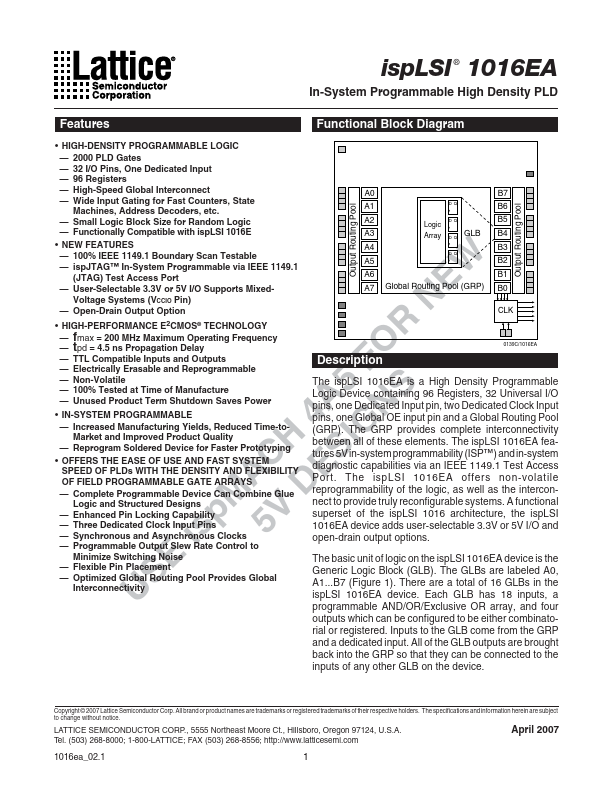

- HIGH-DENSITY PROGRAMMABLE LOGIC

- 2000 PLD Gates

- 32 I/O Pins, One Dedicated Input

- 96 Registers

- High-Speed Global Interconnect

- Wide Input Gating for Fast Counters, State

- Small Logic Block Size for Random Logic

- Functionally patible with ispLSI 1016E

- NEW FEATURES

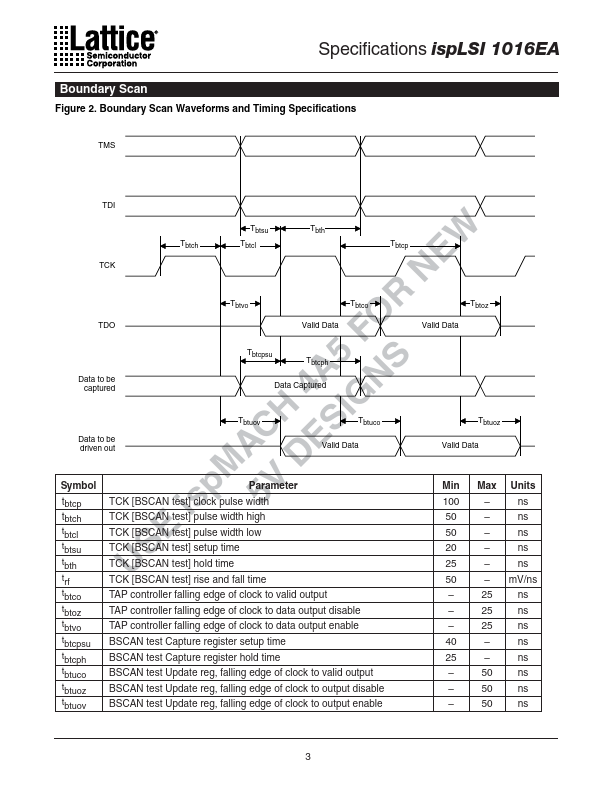

- 100% IEEE 1149.1 Boundary Scan Testable