MACH210-12

MACH210-12 is High-Density EE CMOS Programmable Logic manufactured by Lattice.

- Part of the MACH210A-7 comparator family.

- Part of the MACH210A-7 comparator family.

FINAL

’L: -7/10/12/15/20, Q-12/15/20

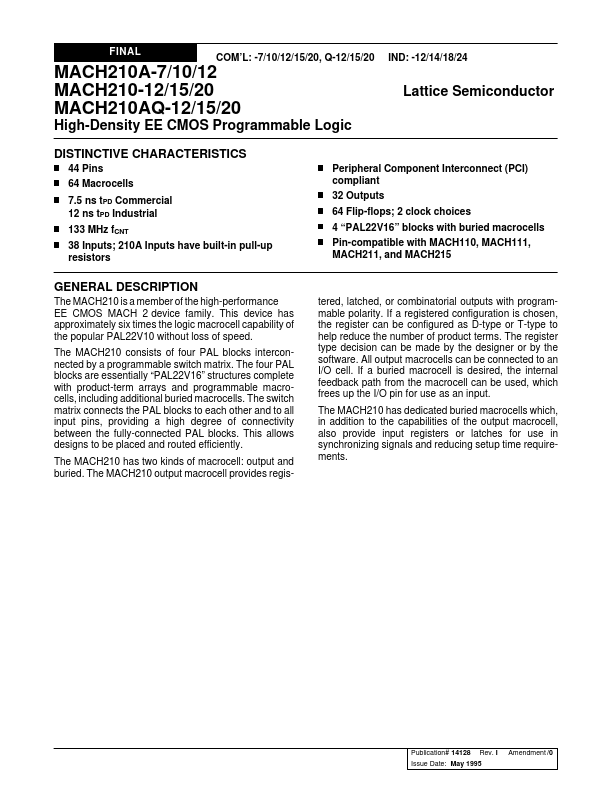

MACH210A-7/10/12

MACH210-12/15/20

MACH210AQ-12/15/20

High-Density EE CMOS Programmable Logic

IND: -12/14/18/24

Lattice Semiconductor

DISTINCTIVE CHARACTERISTICS

44 Pins 64 Macrocells

7.5 ns tPD mercial 12 ns tPD Industrial

133 MHz fCNT 38 Inputs; 210A Inputs have built-in pull-up resistors

Peripheral ponent Interconnect (PCI) pliant

32 Outputs

64 Flip-flops; 2 clock choices

4 “PAL22V16” blocks with buried macrocells

Pin-patible with MACH110, MACH111, MACH211, and MACH215

GENERAL DESCRIPTION

The MACH210 is a member of the high-performance EE CMOS MACH 2 device family. This device has approximately six times the logic macrocell...