LTC2217

LTC2217 is Low Noise ADC manufactured by Linear Technology.

Features

- Sample Rate: 105Msps

- 81.3d BFS Noise Floor

- 100d B SFDR

- SFDR >90d B at 70MHz

- 85fs RMS Jitter

- 2.75VP-P Input Range

- 400MHz Full Power Bandwidth S/H

- Optional Internal Dither

- Optional Data Output Randomizer

- LVDS or CMOS Outputs

- Single 3.3V Supply

- Power Dissipation: 1.19W

- Clock Duty Cycle Stabilizer

- Pin patible with LTC2208

- 64-Pin (9mm × 9mm) QFN Package

APPLICATIONS

- Telemunications

- Receivers

- Cellular Base Stations

- Spectrum Analysis

- Imaging Systems

- ATE

, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Patents Pending.

16-Bit, 105Msps Low Noise ADC DESCRIPTION

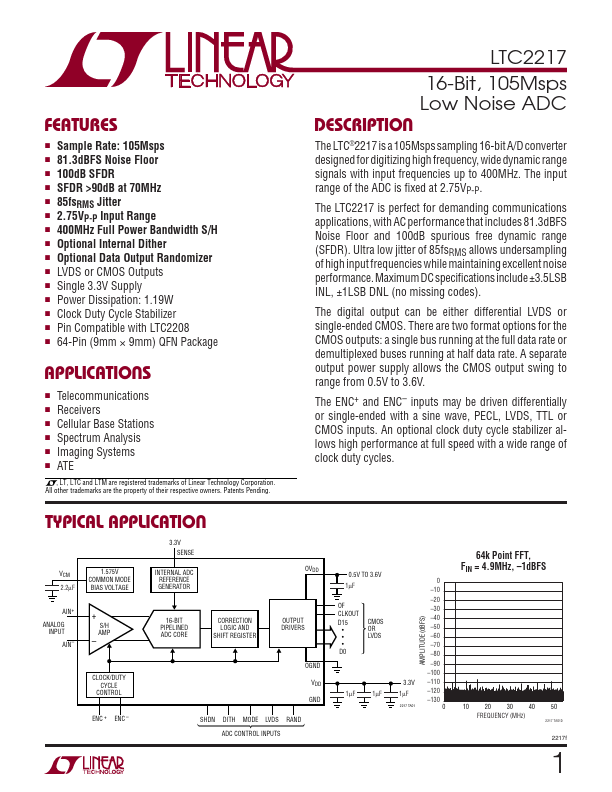

The LTC®2217 is a 105Msps sampling 16-bit A/D converter designed for digitizing high frequency, wide dynamic range signals with input frequencies up to 400MHz. The input range of the ADC is fixed at 2.75VP-P.

The LTC2217 is perfect for demanding munications applications, with AC performance that includes 81.3d BFS Noise Floor and 100d B spurious free dynamic range (SFDR). Ultra low jitter of 85fs RMS allows undersampling of high input frequencies while maintaining excellent noise performance. Maximum DC specifications include ±3.5LSB INL, ±1LSB DNL (no missing codes).

The digital output can be either differential LVDS or single-ended CMOS. There are two format options for the CMOS outputs: a single bus running at the full data rate or demultiplexed buses running at half data rate. A separate output power supply allows the CMOS output swing to range from 0.5V to 3.6V.

The ENC+ and ENC- inputs may be driven differentially or single-ended with a sine wave, PECL, LVDS, TTL or CMOS inputs. An optional clock duty cycle stabilizer allows high performance at full speed with a wide range of clock duty cycles.

TYPICAL...