LTC3831-1

LTC3831-1 is High Power Synchronous Switching Regulator Controller manufactured by Linear Technology.

Features s VOUT as Low as 0.4V s High Power Switching Regulator Controller for DDR Memory Termination s VOUT Tracks 1/2 of VIN or External VREF s No Current Sense Resistor Required s Low VCC Supply: 3V to 8V s Maximum Duty Cycle > 91% Over Temperature s Drives All N-Channel External MOSFETs s High Efficiency: Up to 95% s Programmable Fixed Frequency Operation:

100k Hz to 500k Hz s External Clock Synchronization Operation s Programmable Soft-Start s Low Shutdown Current: <10µA s Overtemperature Protection s Available in 16-PUin Narrow SSOP Package APPLICATIO S s DDR SDRAM Termination s SSTL_2, SSTL_3 Interface s HSTL Interface

High Power Synchronous Switching Regulator Controller for DDR Memory Termination

DESCRIPTIO

The LTC®3831-1 is a high power, high efficiency switching regulator controller designed for DDR memory termination. The LTC3831-1 generates an output voltage equal to 1/2 of an external supply or reference voltage. The LTC3831-1 uses a synchronous switching architecture with N-channel MOSFETs. Additionally, the chip senses output current through the drain-source resistance of the upper N-channel FET, providing an adjustable current limit without a current sense resistor.

The LTC3831-1 operates with input supply voltage as low as 3V and with a maximum duty cycle of > 91%. It includes a fixed frequency PWM oscillator for low output ripple operation. The 300k Hz free-running clock frequency can be externally adjusted or synchronized with an external signal from 100k Hz to above 500k Hz. In shutdown mode, the LTC3831-1 supply current drops to <10µA.

, LTC and LT are registered trademarks of Linear Technology Corporation.

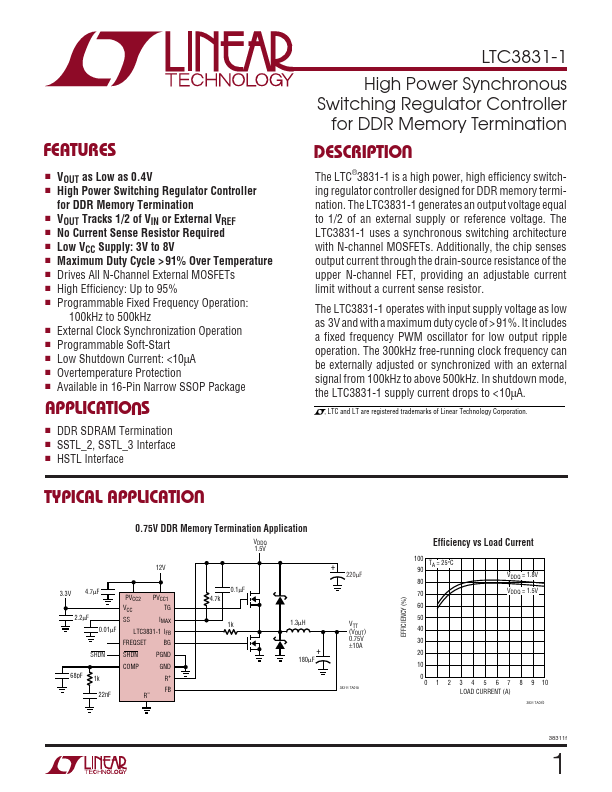

TYPICAL APPLICATIO

0.75V DDR Memory Termination Application

VDDQ 1.5V

12V

3.3V 4.7µF

2.2µF

0.01µF

PVCC2 VCC

PVCC1 TG

IMAX

LTC3831-1 IFB

FREQSET

SHDN

SHDN

PGND

68p F 1k

R+

22n F

R-

0.1µF...